## Communication Locality in Computation: Software, Chip Multiprocessors and Brains

Daniel L. Greenfield

University of Cambridge Computer Laboratory Trinity Hall

April 2010

This dissertation is submitted for the degree of Doctor of Philosophy

#### Declaration

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except where specifically indicated in the text.

This dissertation does not exceed the regulation length of 60 000 words, including tables and footnotes.

#### Note

This dissertation was originally titled 'Rentian Locality in Chip Multiprocessors' at submission.

#### Communication Locality in Computation: Software, Chip Multiprocessors and Brains

Daniel L. Greenfield

#### Summary

This thesis extends techniques from digital circuit interconnect prediction (in particular Rent's rule) to analyse and predict interconnectedness in software, Chip-Multiprocessors (CMP) and Networks-on-Chip (NoC). Since the birth of the microprocessor, transistors have been getting cheaper, faster and more energy efficient, whereas global wires have changed little. At the same time we are moving towards thousands of processing cores on a chip, with software distributed across them. This new era of communication-dominated computing is marked by local computation on a core being cheap, but with global communication between cores and with external memory as expensive. Thus the physical spatial position of software starts to become important. Indeed, it is shown that unless physical locality in communication is exploited, the costs become untenable with technology scaling.

In VLSI (Very Large Scale Integrated) circuits, the fractal connectivity of Rent's rule is a well known predictor of the physical locality of interconnect across many orders of magnitude. It is shown how a generalised Rent's rule can characterise and model both spatial and temporal locality in software, and it is demonstrated that locality effects can be exploited in Network-on-Chip design for fault tolerance. Evidence of Rentian fractal scaling in software is examined across several benchmarks using multiple methods. Given Rentian scaling, many fundamental results are derived for future many-core CMP architectures that relate number of cores, communication, on-chip memory and the Rent's exponent, including some surprising scaling requirements towards fine-grain communication. It is also shown that existing models of an algorithm's asymptotic time and energy cost are inadequate to account for physical communication costs and locality. A new analytical framework that utilises locality and its Rentian characterisation is demonstrated on several example algorithms, and a study is made of the 'embedding problem' for composing embeddings of algorithms together. Finally, in examining the interplay of communication and massively parallel computation at larger scales, we look at the mammalian brain as a proof-of-existence. We show that Rent's rule also appears to apply to neuronal systems, and that this relates to the allometric scaling of communication to computation.

#### Acknowledgements

Over the course of this PhD, I have been honoured to be in the company of many outstanding people. First and foremost, I would like to thank Simon Moore, my supervisor, not only for his invaluable feedback, but for his enduring support of these blue-sky research ideas. Thanks also go to Robert Mullins for many stimulating conversations, as well as to Alan Mycroft and PhD examiners Steve Furber and David Greaves for their insightful feedback.

For an incredible journey of collaboration, I'd like to thank Danielle Bassett and Ed Bullmore whose sheer enthusiasm have made it all the more enjoyable. For taking on the Herculean task of checking through proofs, I am particularly grateful for Stéphanie Jacquot's help. Thanks also go to Jeong-gun Lee for many fascinating discussions in my first year, and to Nick Barrow-Williams and Chris Fensch for their research support. I also wish to thank colleagues Arnab Banerjee, Rosemary Francis and Andrew West for many pleasurable discussions at the lab. To Alban Rrustemi, I am truly indebted for all his invaluable help, feedback and moral support.

For all her enduring support through the difficult times of producing this, and all the absurd fun we've had in between, I'd like to thank Rei Kanemura.

My deep appreciation also goes to the Gates community and Trinity Hall, for all the treasured friendships and moments over these years.

This work was generously supported by a scholarship from the Gates Cambridge Trust, who I would like to thank not just for their financial support, but also the fervent intellectual community that they have fostered.

Finally, but certainly not least, I thank my parents who were excited to see me take on this challenge, and realise a long-held childhood dream. I thoroughly blame my father's genes for making me all-too fascinated by science and technology and the spirit of tackling the supposedly impossible. I hope that the ideas here will one-day result in even cooler gadgets for him to play with. But in all seriousness, I would like to deeply thank them both for laying down a foundation of a good education. And especially to my mother, I would like to thank her for all her love and support, and for always encouraging me to pursue my dreams, wherever they may take me.

## CONTENTS

|   | Glos  | sary                                             | 17 |

|---|-------|--------------------------------------------------|----|

| 1 | Intro | oduction                                         | 19 |

|   | 1.1   | Overview                                         | 19 |

|   | 1.2   | Main Contributions                               | 19 |

|   | 1.3   | Organisation                                     | 22 |

|   | 1.4   | Publications                                     | 25 |

| 2 | Mot   | ivations: communication vs. computation          | 27 |

|   | 2.1   | Broken assumptions: no escape from Physics       | 27 |

|   | 2.2   | The many-core memory bandwidth wall              | 29 |

|   | 2.3   | Networks-on-Chip and traffic patterns            | 32 |

|   | 2.4   | New interconnect technologies                    | 35 |

|   |       | 2.4.1 Optical                                    | 35 |

|   |       | 2.4.2 LVDS transmission lines                    | 36 |

|   |       | 2.4.3 Carbon Nanotubes                           | 37 |

|   |       | 2.4.4 Surface plasmon resonance                  | 37 |

|   | 2.5   | Summary                                          | 37 |

| 3 | Bacl  | sground                                          | 39 |

|   | 3.1   | High-performance computing                       | 39 |

|   | 3.2   | Existing models of parallelism and communication | 40 |

|   |       | 3.2.1 PRAM model                                 | 40 |

|   |       | 3.2.2 BSP model                                  | 40 |

|   |       | 3.2.3 LogP model                                 | 41 |

|   |       | 3.2.4 D-BSP model                                | 41 |

|   |       | 3.2.5 Multi-BSP model                            | 42 |

|   |       | 3.2.6 A note on Amdahl's law                     | 42 |

|   | 3.3   | Communication complexity approaches              | 43 |

|   |     | 3.3.1    | Yao's two-party and multi-party models   | 43       |

|---|-----|----------|------------------------------------------|----------|

|   |     | 3.3.2    | Thompson's area-time complexity          | 44       |

|   |     | 3.3.3    | Leiserson's layout analysis              | 44       |

|   |     | 3.3.4    | Bilardi's analysis                       | 44       |

|   |     | 3.3.5    | Fox's analysis                           | 45       |

|   | 3.4 | Rentia   | an scaling                               | 45       |

|   |     | 3.4.1    | Regions I, II and III                    | 46       |

|   |     | 3.4.2    | Application                              | 46       |

|   |     | 3.4.3    | Topological vs. Physical Rentian scaling | 47       |

|   |     | 3.4.4    | A-priori wire estimation                 | 48       |

|   |     | 3.4.5    | Fractal dimensionality                   | 48       |

|   | 3.5 | Summ     | ary                                      | 49       |

| 4 | Dom | tion los | ality for Networks on Chin               | 51       |

| 4 |     |          | ality for Networks-on-Chip               |          |

|   | 4.1 |          | ding Rent's Rule for NoC                 | 52<br>52 |

|   |     | 4.1.1    | Argument                                 | 52       |

|   |     | 4.1.2    | Comparing VLSI with NoC                  | 52       |

|   |     | 4.1.3    | Derivation                               | 53       |

|   | 4.0 | 4.1.4    | Comparison to classical Rent's Rule      | 55       |

|   | 4.2 |          | al Implications                          | 56       |

|   |     | 4.2.1    | Hop-length distributions                 | 56       |

|   |     | 4.2.2    | Implications for scaling                 | 58       |

|   |     | 4.2.3    | Prior work                               | 59       |

|   |     | 4.2.4    | Hot-spots                                | 59       |

|   | 4.3 |          | ed to Fault Tolerance in NoC             | 60       |

|   |     | 4.3.1    | Distributions Models                     | 60       |

|   | 4.4 |          | t-tolerant router design                 | 63       |

|   |     | 4.4.1    | Router-activity distributions            | 67       |

|   |     | 4.4.2    | Fault tolerance analyses                 | 68       |

|   |     |          | 4.4.2.1 Unreachability analysis          | 69       |

|   | 4.5 | Conclu   | usions                                   | 74       |

| 5 | Exp | eriment   | al evidence for Rent's rule                                          | 77  |

|---|-----|-----------|----------------------------------------------------------------------|-----|

|   | 5.1 | Other     | work: Heirman et al                                                  | 78  |

|   | 5.2 | Evider    | nce in simulated CMP experiments                                     | 79  |

|   |     | 5.2.1     | Caution: the uniform-traffic model                                   | 80  |

|   |     | 5.2.2     | Methodology                                                          | 81  |

|   |     | 5.2.3     | Results                                                              | 83  |

|   |     | 5.2.4     | Discussion                                                           | 86  |

|   | 5.3 | Evider    | nce in dynamic data-dependency-graphs                                | 88  |

|   |     | 5.3.1     | Earlier work on fractal properties in software                       | 88  |

|   |     | 5.3.2     | Fractal behaviour in software                                        | 89  |

|   |     | 5.3.3     | Box-counting dimension                                               | 90  |

|   |     | 5.3.4     | Methodology                                                          | 92  |

|   |     | 5.3.5     | Results                                                              | 93  |

|   |     | 5.3.6     | Dimensionality of communication vs. parallelism                      | 94  |

|   | 5.4 | Rentia    | in analysis of dynamic-data-dependency graphs                        | 94  |

|   |     | 5.4.1     | Temporal communication and approximate distributions                 | 96  |

|   |     | 5.4.2     | Physical (embedded) analysis                                         | 98  |

|   |     | 5.4.3     | Topological analysis                                                 | 102 |

|   | 5.5 | Conclu    | usion                                                                | 103 |

| 6 | Gen | eralising | g Rent's rule                                                        | 107 |

|   | 6.1 | The p     | rinciple of cost universality                                        | 108 |

|   | 6.2 | Provin    | ng asymptotic equivalence of Rent's rule and power-law distance dis- |     |

|   |     | tributi   | ons                                                                  | 110 |

|   |     | 6.2.1     | Lemmas proving properties of $\theta(L)$                             | 112 |

|   |     | 6.2.2     | Rent's rule from continuous power-law tails                          | 117 |

|   |     | 6.2.3     | Rent's rule from discrete power-law tails                            | 120 |

|   |     | 6.2.4     | Rent's rule from finite distribution lengths                         | 125 |

|   |     | 6.2.5     | Uniqueness of exact solutions                                        | 126 |

|   |     | 6.2.6     | Internal Edge Length Distribution                                    | 128 |

|   | 6.3 | Fracta    | l embeddings into arbitrary spaces                                   | 128 |

|   |     | 6.3.1     | Invariant property of embeddings                                     | 128 |

|   | 6.4 | Conclu    | usion                                                                | 131 |

|   |     | 6.4.1     | An intuitive example: human-interaction networks                     | 132 |

| 7 | Spat        | io-temp                                                                                                    | ooral Rentian model: CMP scaling implications                      | 133                                                                                                                                                       |

|---|-------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7.1         | The m                                                                                                      | any-core memory bandwidth wall                                     | 133                                                                                                                                                       |

|   |             | 7.1.1                                                                                                      | The spatio-temporal Rentian model                                  | 133                                                                                                                                                       |

|   |             | 7.1.2                                                                                                      | Summary of Key Results                                             | 135                                                                                                                                                       |

|   | 7.2         | Rentia                                                                                                     | In many-core architecture                                          | 137                                                                                                                                                       |

|   |             | 7.2.1                                                                                                      | Configuration-space analysis for the 2-D mesh                      | 137                                                                                                                                                       |

|   |             | 7.2.2                                                                                                      | Separating Spatial and Temporal components                         | 140                                                                                                                                                       |

|   | 7.3         | Rentia                                                                                                     | an memory and external I/O bandwidth                               | 142                                                                                                                                                       |

|   |             | 7.3.1                                                                                                      | Many-core scaling                                                  | 144                                                                                                                                                       |

|   |             | 7.3.2                                                                                                      | Accounting for costly spatial communication                        | 148                                                                                                                                                       |

|   |             | 7.3.3                                                                                                      | Alternate Topologies                                               | 153                                                                                                                                                       |

|   |             | 7.3.4                                                                                                      | Real caches versus Rentian memory                                  | 154                                                                                                                                                       |

|   |             | 7.3.5                                                                                                      | Area & bandwidth constrained many-core scaling                     | 156                                                                                                                                                       |

|   |             | 7.3.6                                                                                                      | Shortcomings of the model                                          | 160                                                                                                                                                       |

|   | 7.4         | Concl                                                                                                      | usion                                                              | 161                                                                                                                                                       |

|   |             |                                                                                                            |                                                                    |                                                                                                                                                           |

| 8 | Effe        | ct of Lo                                                                                                   | ocality on Asymptotic Complexity                                   | 163                                                                                                                                                       |

| 8 | Effe<br>8.1 |                                                                                                            | ocality on Asymptotic Complexity<br>Rentian analysis of algorithms |                                                                                                                                                           |

| 8 |             |                                                                                                            |                                                                    |                                                                                                                                                           |

| 8 |             | Direct                                                                                                     | Rentian analysis of algorithms                                     | 163<br>164                                                                                                                                                |

| 8 |             | Direct<br>8.1.1<br>8.1.2                                                                                   | Rentian analysis of algorithms                                     | 163<br>164<br>164                                                                                                                                         |

| 8 |             | Direct<br>8.1.1<br>8.1.2                                                                                   | Rentian analysis of algorithms                                     | 163<br>164<br>164<br>165                                                                                                                                  |

| 8 |             | Direct<br>8.1.1<br>8.1.2<br>8.1.3                                                                          | Rentian analysis of algorithms                                     | 163<br>164<br>164<br>165<br>166                                                                                                                           |

| 8 |             | Direct<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4                                                                 | Rentian analysis of algorithms                                     | <ol> <li>163</li> <li>164</li> <li>164</li> <li>165</li> <li>166</li> <li>166</li> </ol>                                                                  |

| 8 |             | Direct<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6                                               | Rentian analysis of algorithms                                     | <ol> <li>163</li> <li>164</li> <li>164</li> <li>165</li> <li>166</li> <li>166</li> <li>167</li> </ol>                                                     |

| 8 | 8.1         | Direct<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6                                               | Rentian analysis of algorithms                                     | <ol> <li>163</li> <li>164</li> <li>165</li> <li>166</li> <li>166</li> <li>167</li> <li>168</li> </ol>                                                     |

| 8 | 8.1         | Direct<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>The 'e                                     | Rentian analysis of algorithms                                     | <ol> <li>163</li> <li>164</li> <li>165</li> <li>166</li> <li>166</li> <li>167</li> <li>168</li> <li>170</li> </ol>                                        |

| 8 | 8.1         | Direct<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>The 'e<br>8.2.1                            | Rentian analysis of algorithms                                     | <ol> <li>163</li> <li>164</li> <li>165</li> <li>166</li> <li>166</li> <li>167</li> <li>168</li> <li>170</li> <li>175</li> </ol>                           |

| 8 | 8.1         | Direct<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>The 'e<br>8.2.1<br>8.2.2                   | Rentian analysis of algorithms                                     | <ol> <li>163</li> <li>164</li> <li>165</li> <li>166</li> <li>166</li> <li>167</li> <li>168</li> <li>170</li> <li>175</li> <li>176</li> </ol>              |

| 8 | 8.1         | Direct<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>The 'e<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4 | Rentian analysis of algorithms                                     | <ol> <li>163</li> <li>164</li> <li>165</li> <li>166</li> <li>166</li> <li>167</li> <li>168</li> <li>170</li> <li>175</li> <li>176</li> <li>176</li> </ol> |

| 9  | Rent  | ian scaling in neuronal networks                                  | 181  |

|----|-------|-------------------------------------------------------------------|------|

|    | 9.1   | Clarifying the collaboration                                      | 182  |

|    | 9.2   | Datasets and their limitations                                    | 183  |

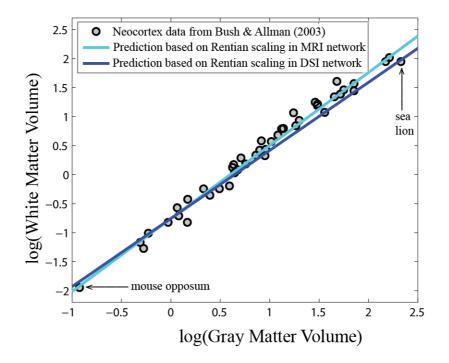

|    | 9.3   | Allometric scaling                                                | 184  |

|    | 9.4   | Methodology                                                       | 187  |

|    |       | 9.4.1 Re-wired networks                                           | 188  |

|    |       | 9.4.2 Non-power-law null hypotheses                               | 188  |

|    | 9.5   | Small World vs. Rentian Fractality                                | 188  |

|    | 9.6   | Results                                                           | 191  |

|    |       | 9.6.1 Topological properties                                      | 191  |

|    |       | 9.6.2 Physical Rentian scaling                                    | 194  |

|    | 9.7   | Prior work                                                        | 196  |

|    |       | 9.7.1 Allometric scaling derivations                              | 199  |

|    | 9.8   | Conclusion                                                        | 199  |

| 10 | Con   | clusions and Future Work                                          | 201  |

| 10 |       | Future Work                                                       |      |

|    | 10.1  |                                                                   | 203  |

| A  | Spati | al Scaling: CMP Software                                          | i    |

| В  | Frac  | tal Dimensionality: MiBench Software                              | ix   |

| С  | Tem   | poral Scaling: MiBench Software                                   | xiii |

| D  | Parti | tioned Scaling: MiBench Software                                  | xxi  |

| E  | Spati | io-Temporal Rentian Model: 32-core system                         | xxix |

| F  | Sour  | ce code for numerical evaluation of Spatio-Temporal Rentian Model | xxxi |

## LIST OF FIGURES

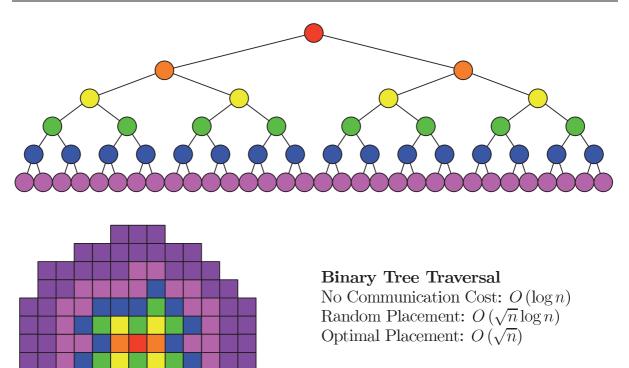

| 2.1  | Algorithms and data-structures must be physically embedded in space (here the 2-D space on-chip). Asymptotic tree traversal costs are shown for binary tree placements, assuming that traversal costs are proportional to distance                                                                                              |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

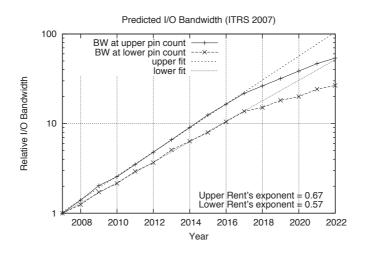

| 2.2  | ITRS I/O Bandwidth Growth                                                                                                                                                                                                                                                                                                       |

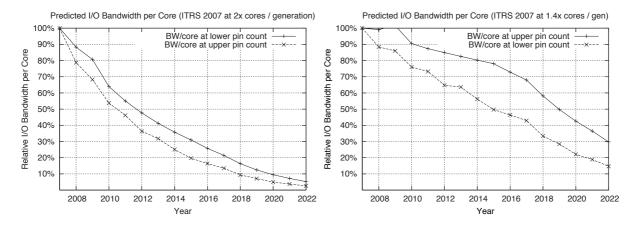

| 2.3  | Predicted scaling of I/O Bandwidth per Core using ITRS numbers, based on 2x cores per generation or 1.4x cores per generation                                                                                                                                                                                                   |

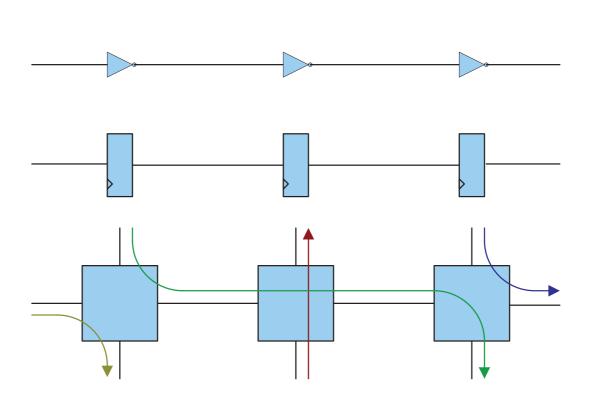

| 2.4  | Virtualisation of interconnect. From wires, to buffered wires, to registered wires, to Networks-<br>on-Chip                                                                                                                                                                                                                     |

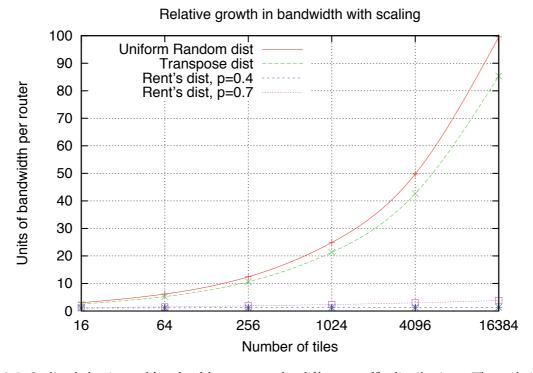

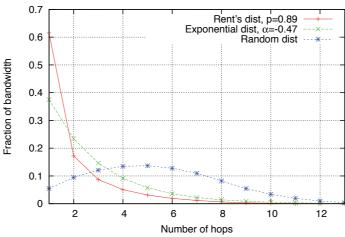

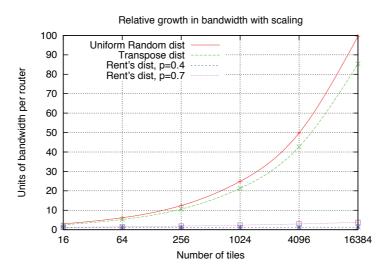

| 2.5  | Scaling behaviour of <i>bandwidth per router</i> for different traffic distributions. The scale is such that, on average, one unit of bandwidth is generated per tile                                                                                                                                                           |

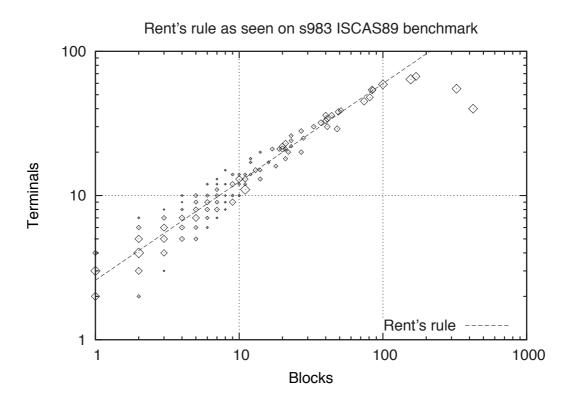

| 3.1  | Example of Rentian scaling on a benchmark VLSI circuit. This figure is modified after Stroobandt's original paper [97]. Note the presence of a Region II near the chip-level scale. The average behaviour of Blocks (i.e. gates) to Terminals is a power-law in the main Region I. 47                                           |

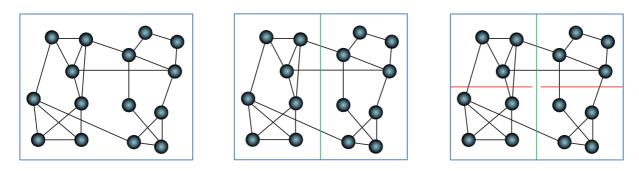

| 3.2  | Two levels of min-cut bi-partitioning (green, then red) applied to a sample graph 48                                                                                                                                                                                                                                            |

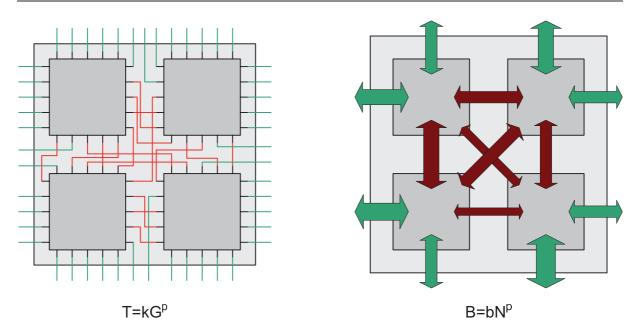

| 4.1  | Rentian scaling in different domains. In VLSI the Rent's exponent characterises the locality of external wires (green) to total wires (red and green) at each level of the hierarchy. In NoC, the wires are replaced with packets, and the Rent's exponent characterises the locality of packets at each level of the hierarchy |

| 4.2  | Three distributions fitted to a semi-random task-graph                                                                                                                                                                                                                                                                          |

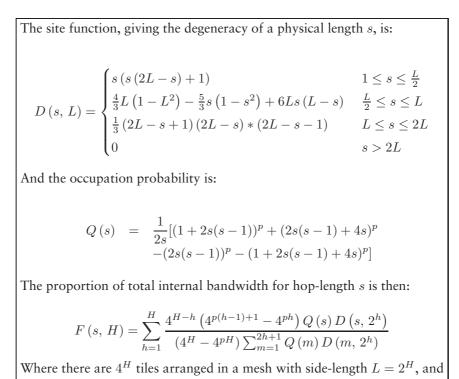

| 4.3  | Equations describing Christie and Stroobandt's equally optimised partitioning and place-<br>ment model [29]                                                                                                                                                                                                                     |

| 4.4  | Scaling behaviour of bandwidth per router for different traffic distributions. The scale is such that, on average, one unit of bandwidth is generated per tile                                                                                                                                                                  |

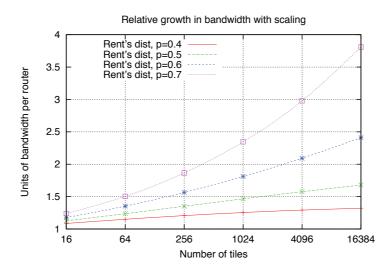

| 4.5  | Relative bandwidth per router for different Rent's exponents as the number of tiles grows.<br>The scale is such that, on average, one unit of bandwidth is generated per tile                                                                                                                                                   |

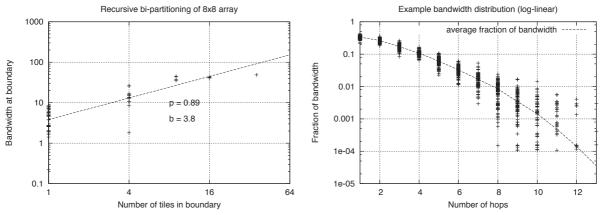

| 4.6  | Rentian best-fit and resultant hop-distribution                                                                                                                                                                                                                                                                                 |

| 4.7  | Plot of tiles unreachable from a source tile due to faults $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 65$                                                                                                                                                                                                         |

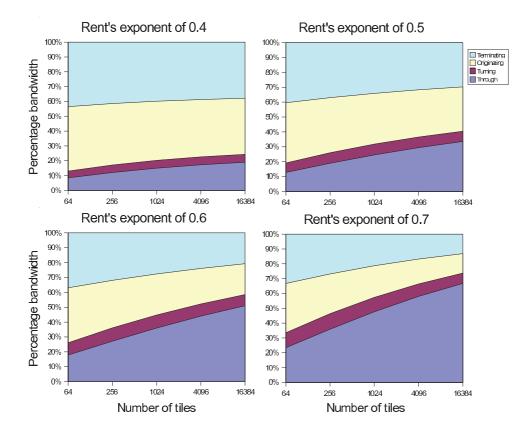

| 4.8  | Expected distribution of router traffic for a working tile, for systems with Rent's exponent ranging from 0.4 to 0.7                                                                                                                                                                                                            |

| 4.9  | Plots of task-link unreachability for three hop-length distributions $\ldots \ldots \ldots \ldots \ldots 71$                                                                                                                                                                                                                    |

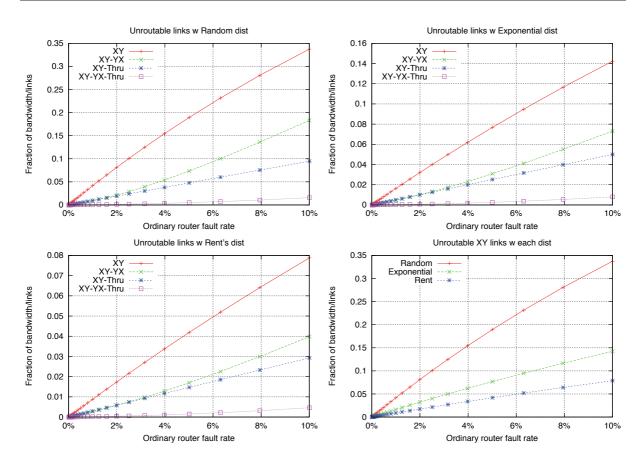

| 4.10 | Collateral effects of a fault on router activity. The fault is located at the middle, and the shade indicates the change in activity of surrounding routers due to re-routing of paths that should have gone through the faulty router                                                                                          |

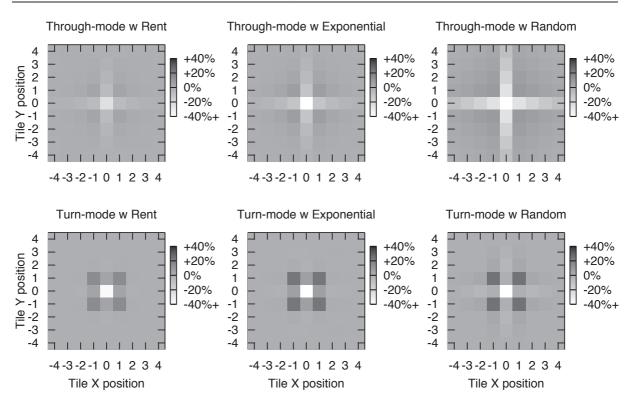

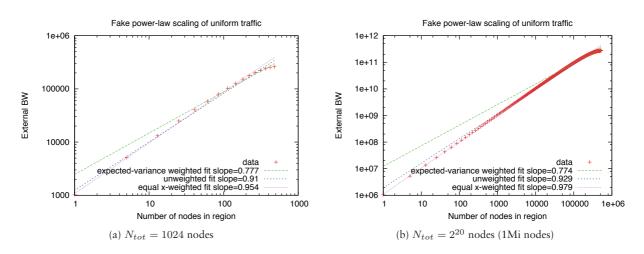

| 5.1  | Example of 'fake' power-law appearance in scaling with uniform traffic for 1024 and 1Mi nodes                                                                                                                                                                                                                                   |

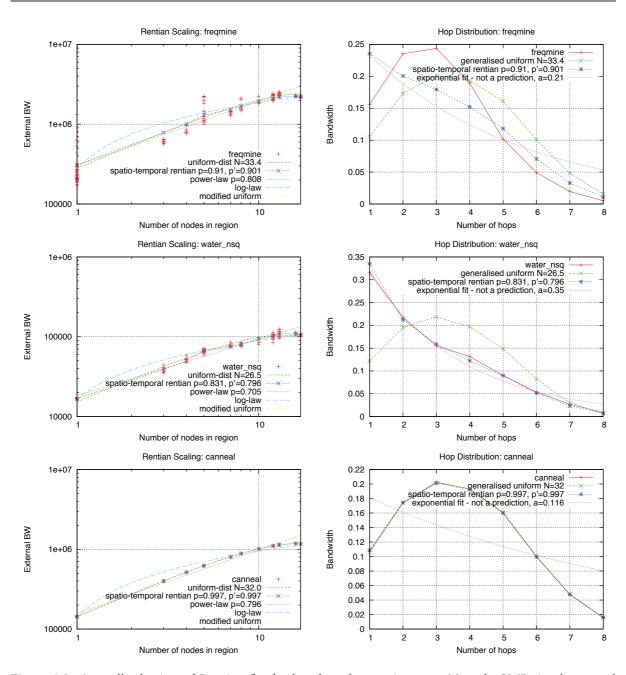

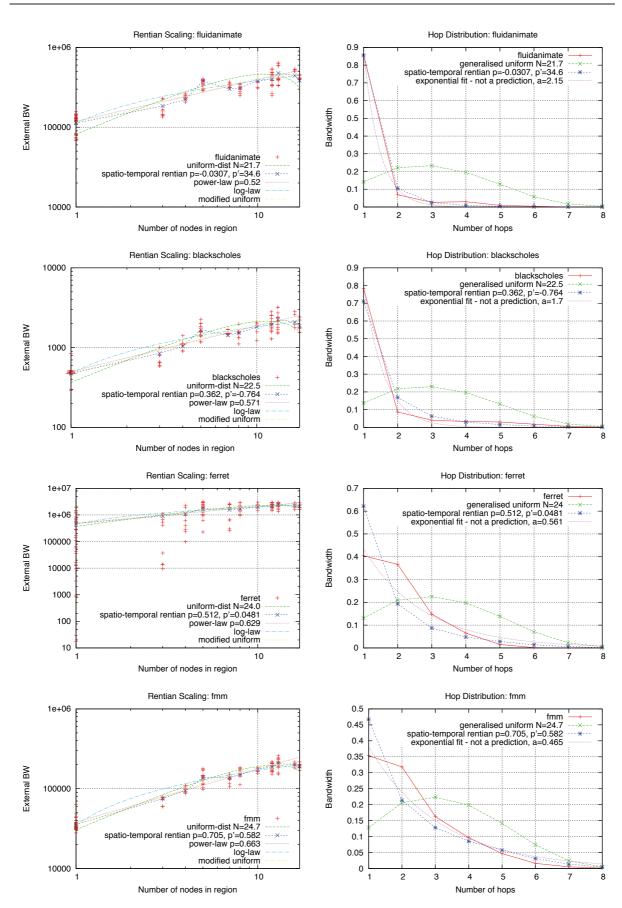

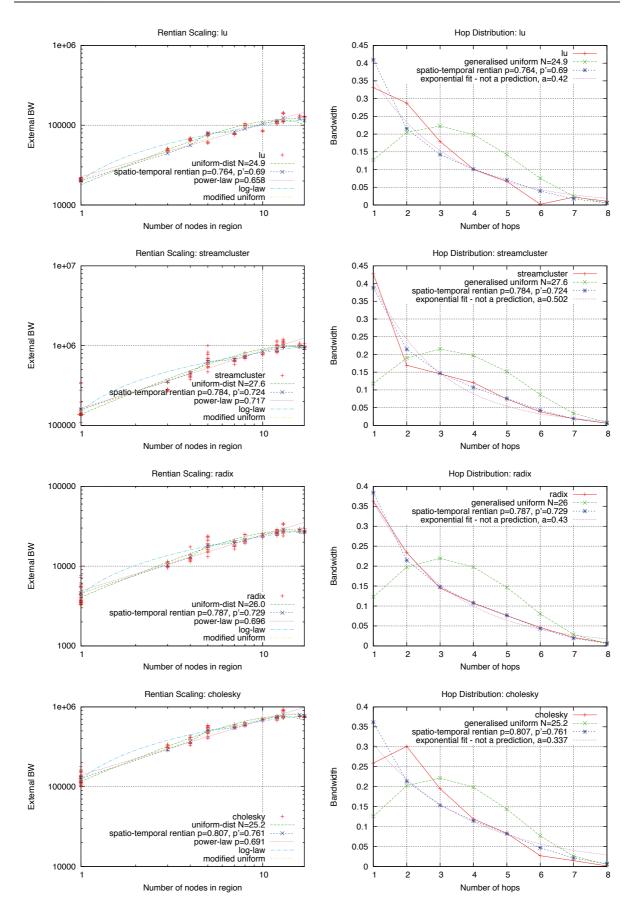

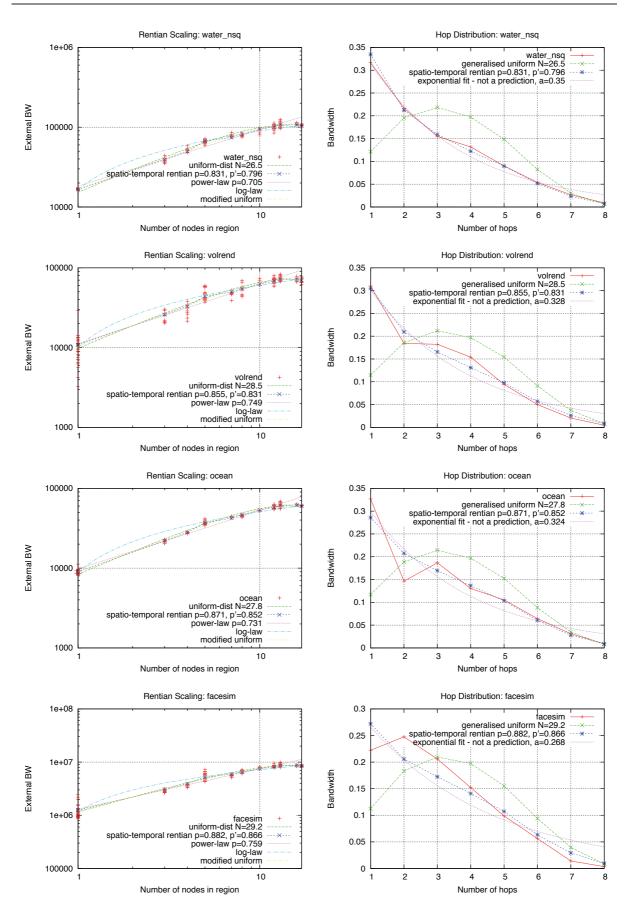

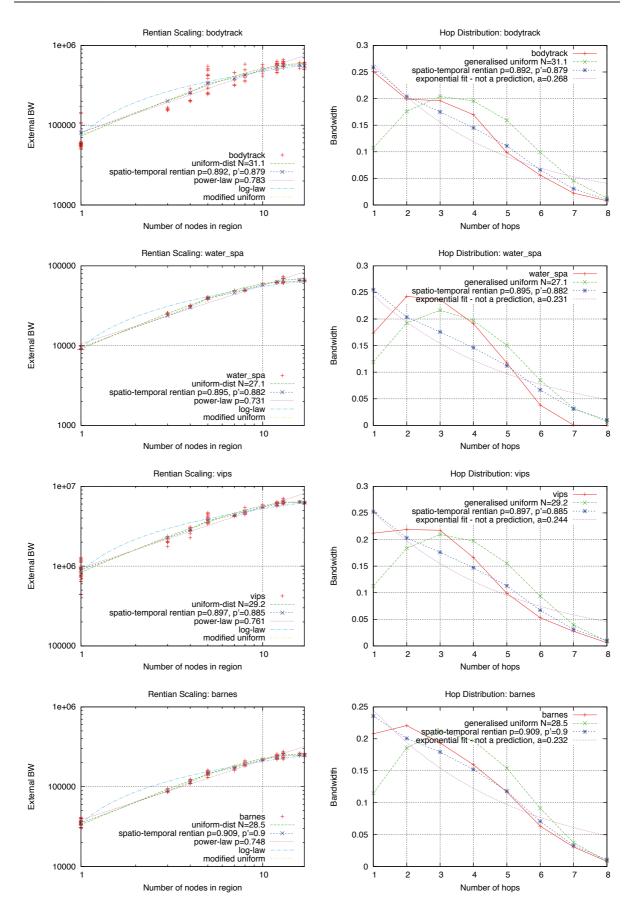

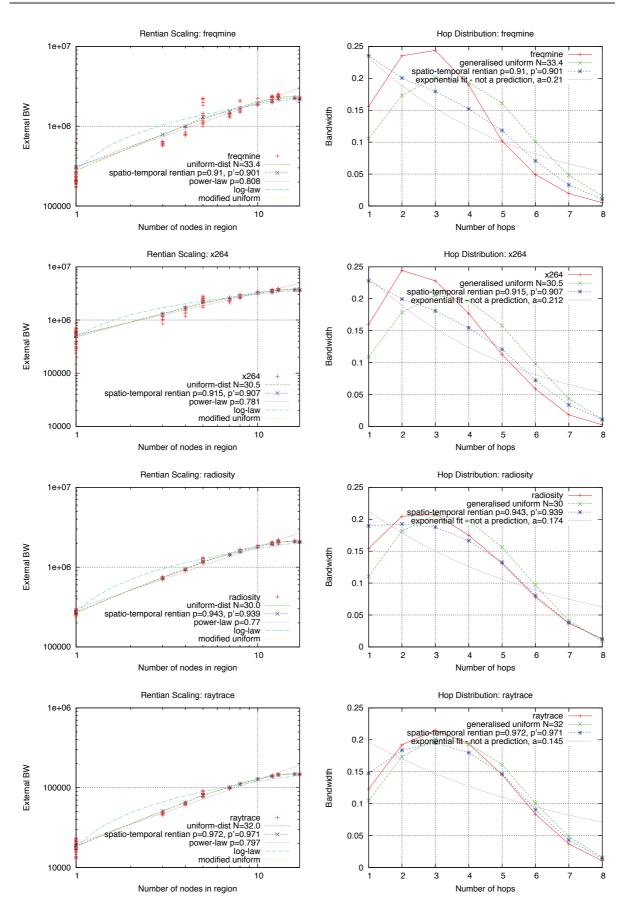

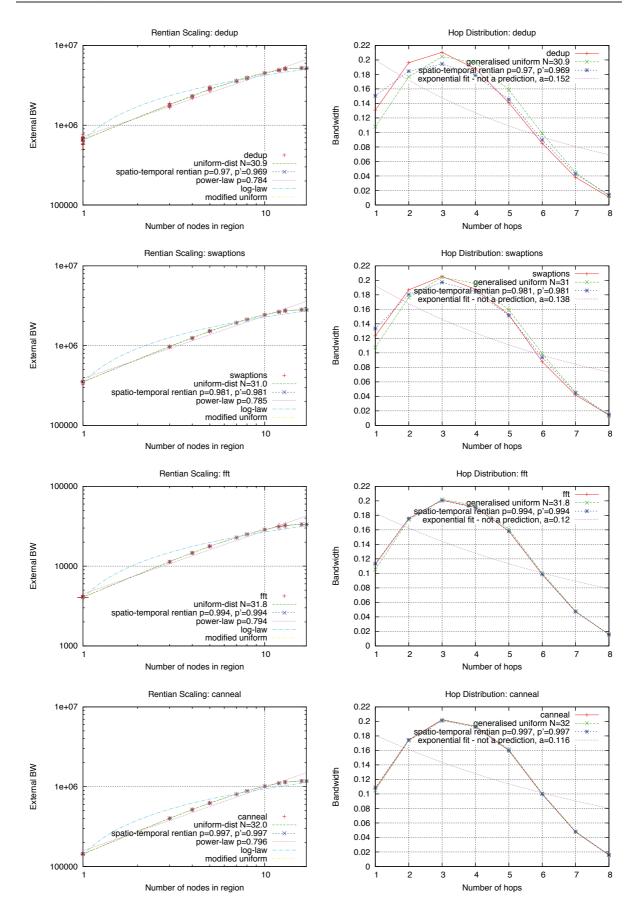

| 5.2  | A small selection of Rentian fits for benchmarks running on a 32-node CMP simulator, and their resultant predicted hop-distributions. While <i>freqmine</i> has an almost equally poor Rentian prediction compared to the uniform model, <i>water_nsq</i> is very close, and <i>canneal</i> has a limiting-case behaviour of uniform traffic in the Rentian model ( $p \approx 1$ implying no locality). For a comprehensive set please see Appendix A |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

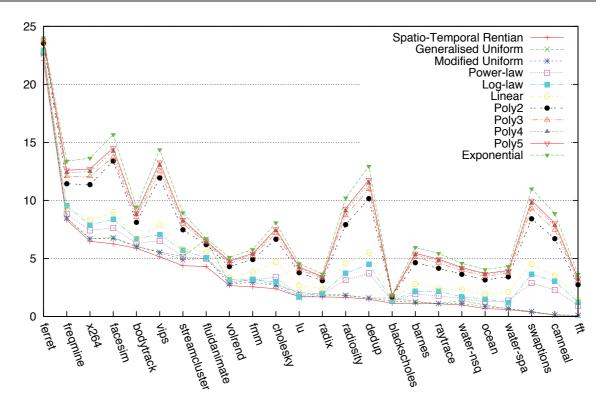

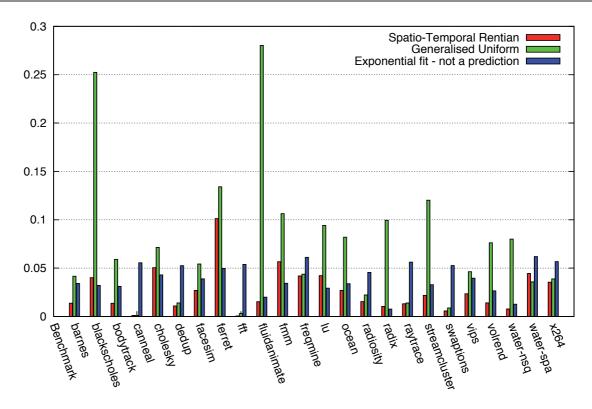

| 5.3  | RMS error (including data's variance) of BW versus node fits                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.4  | RMS error (excluding data's variance) of BW versus node fits                                                                                                                                                                                                                                                                                                                                                                                           |

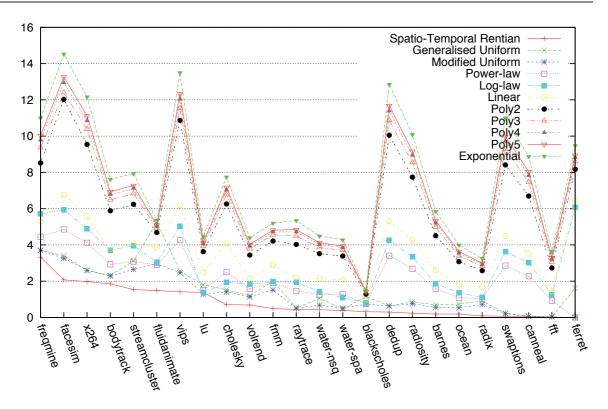

| 5.5  | Hop-distribution RMS prediction errors (based on Bandwidth vs. Nodes scaling fits) 87                                                                                                                                                                                                                                                                                                                                                                  |

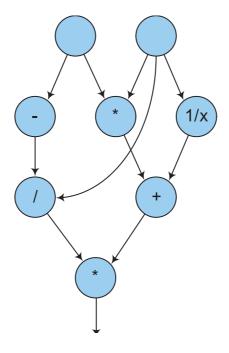

| 5.6  | Example of a Data-Dependency Graph                                                                                                                                                                                                                                                                                                                                                                                                                     |

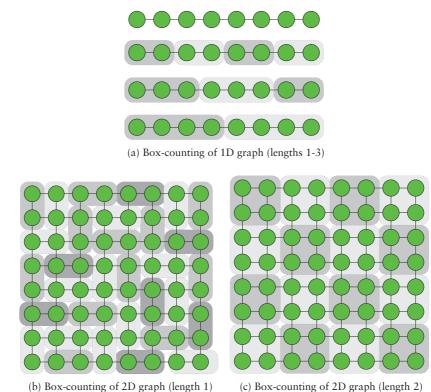

| 5.7  | Box-counting of example 1D and 2D graphs                                                                                                                                                                                                                                                                                                                                                                                                               |

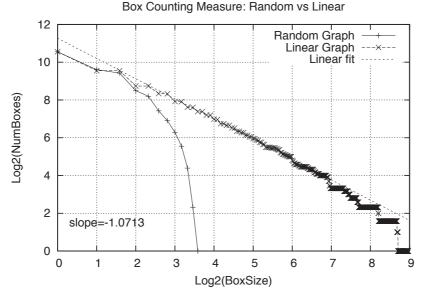

| 5.8  | Box-counting measure comparing a Random Erdös-Rènyi graph to a linear graph, each with 1500 nodes                                                                                                                                                                                                                                                                                                                                                      |

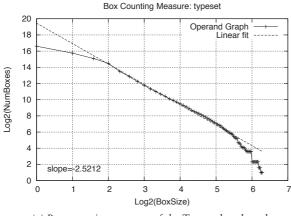

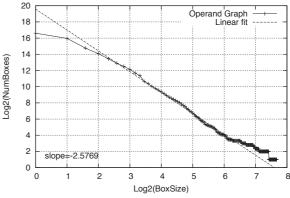

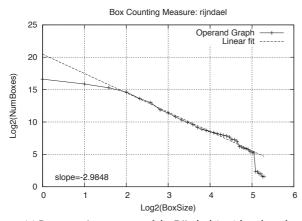

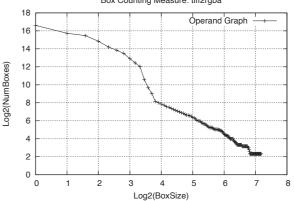

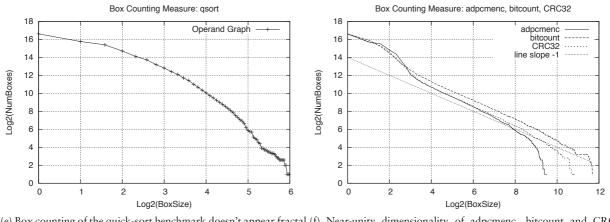

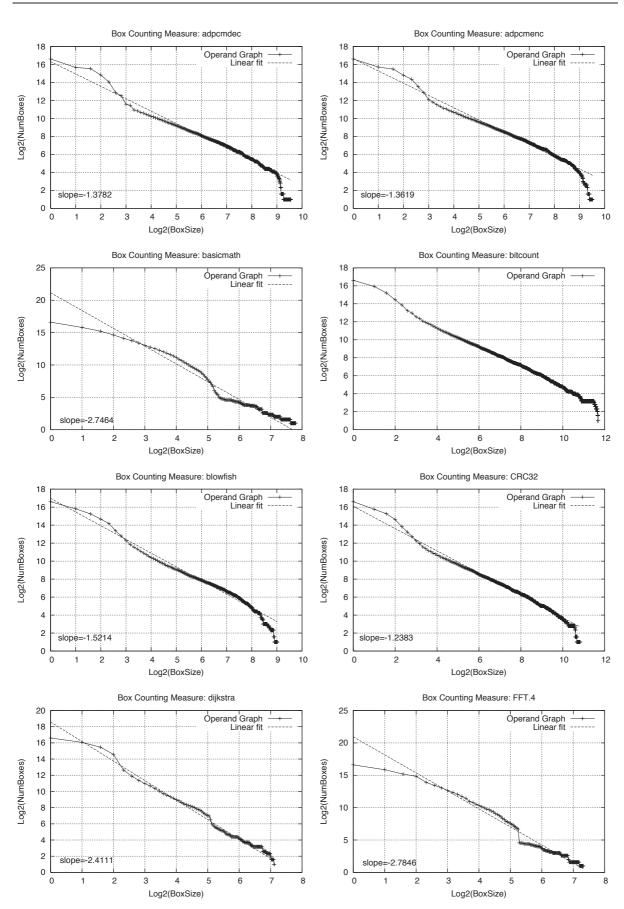

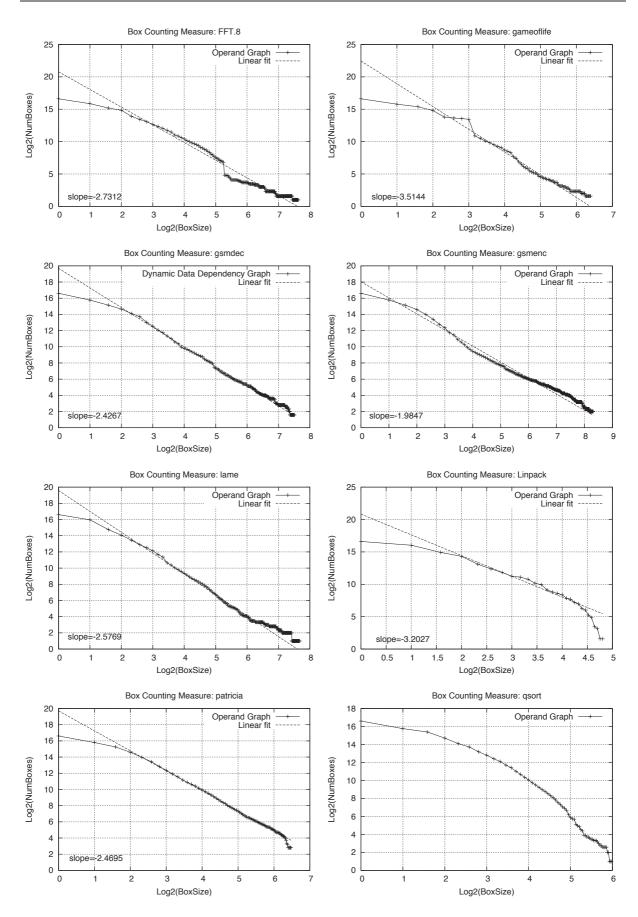

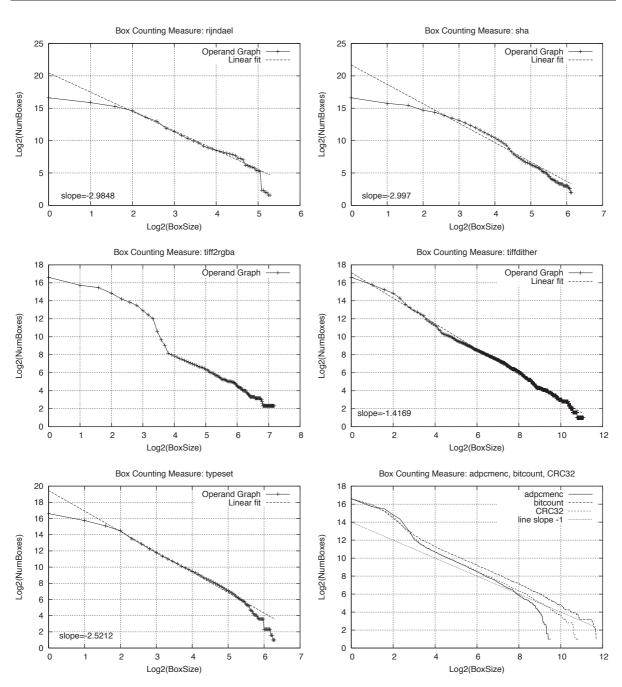

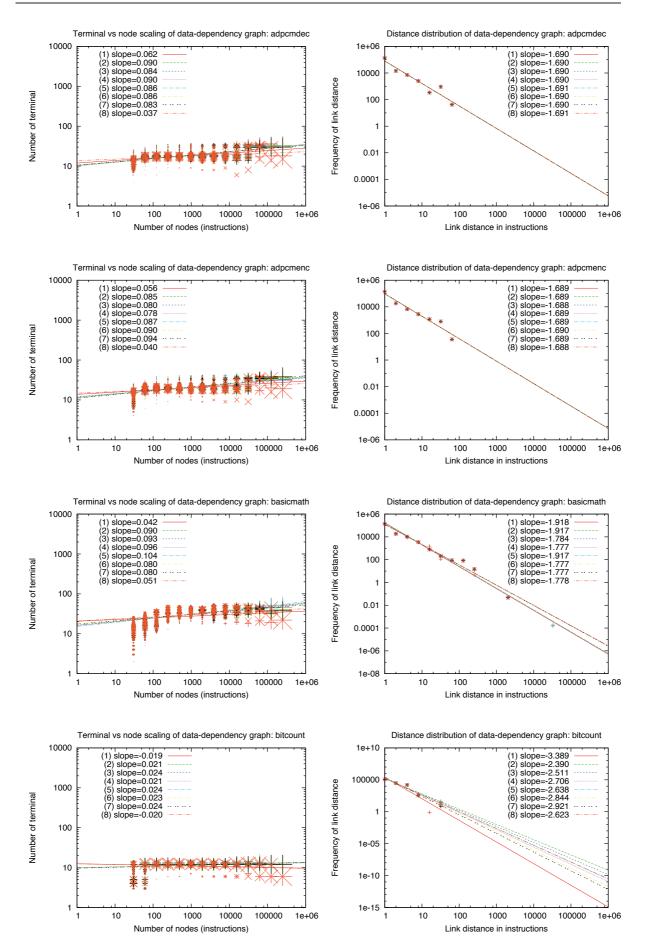

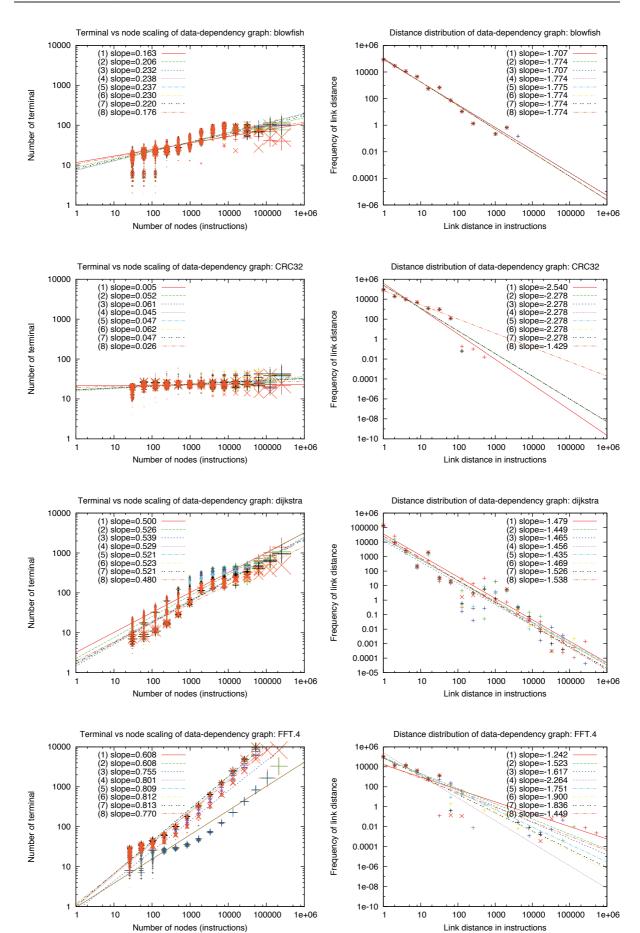

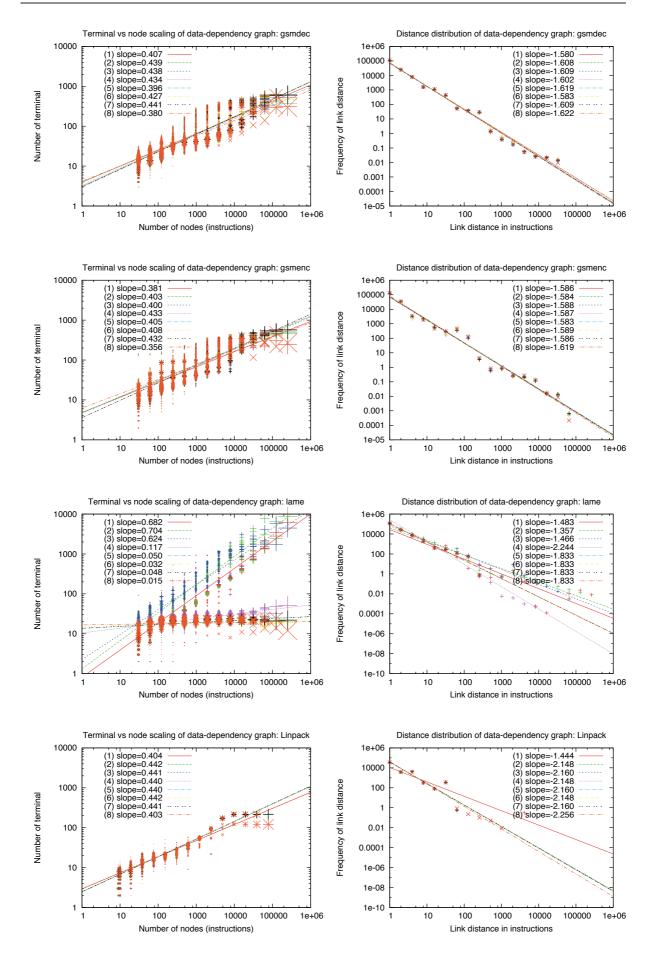

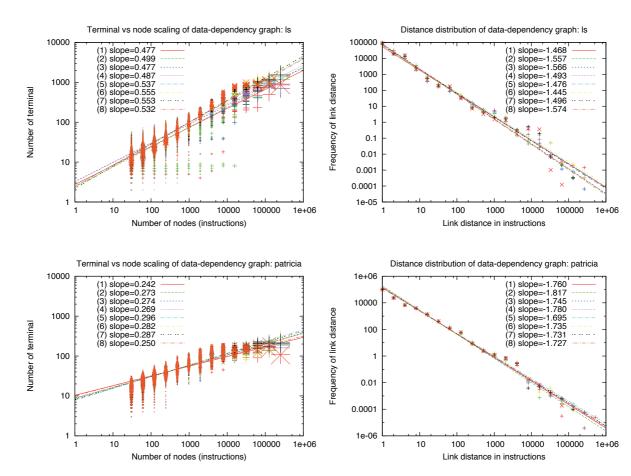

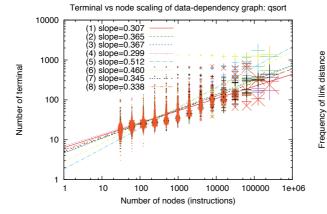

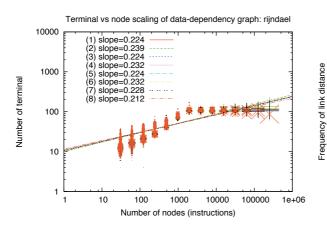

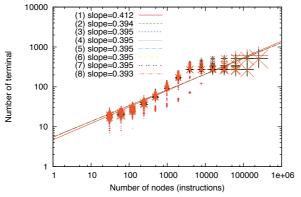

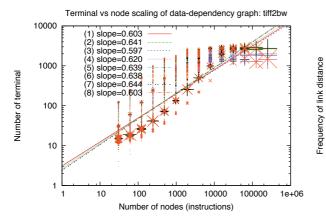

| 5.9  | A selection of box-counting plots from the MiBench benchmark suite. For a complete set, please refer to Appendix B                                                                                                                                                                                                                                                                                                                                     |

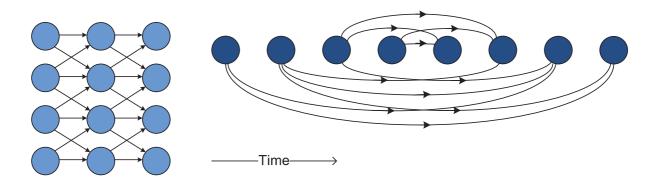

| 5.10 | Temporal Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                  |

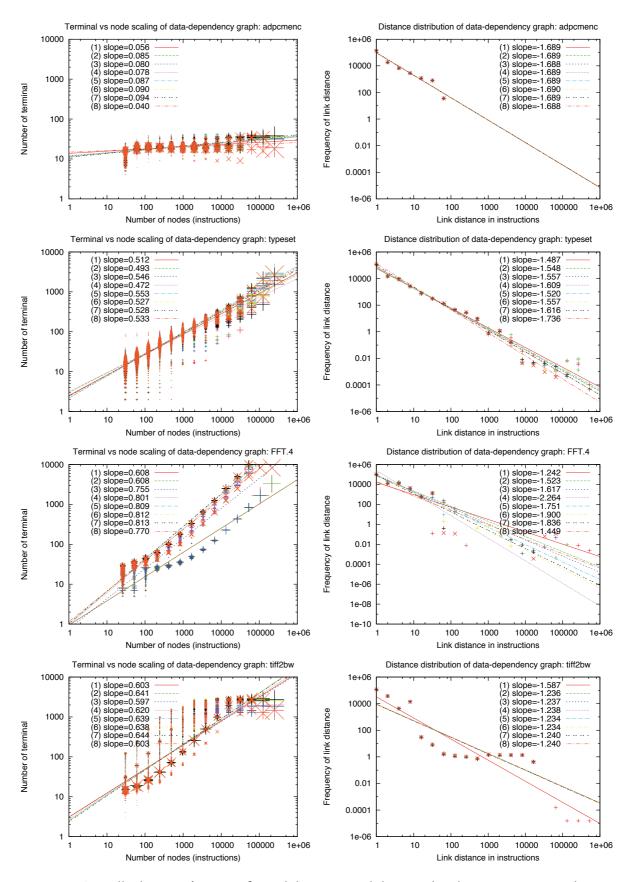

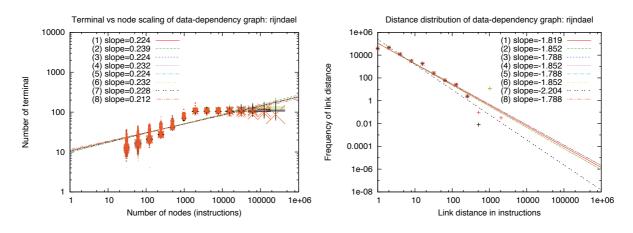

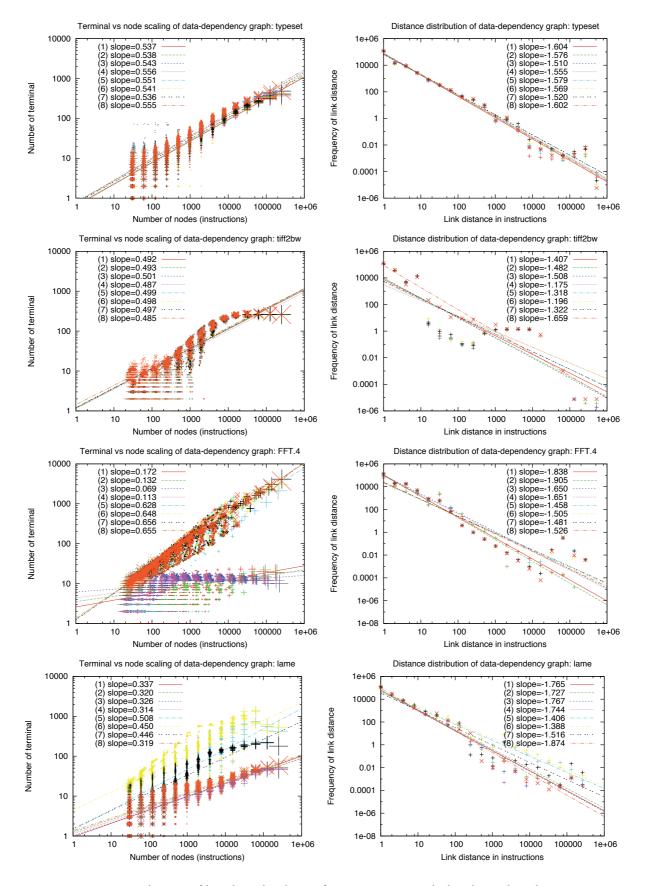

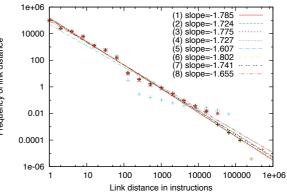

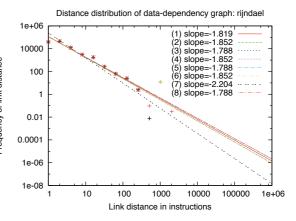

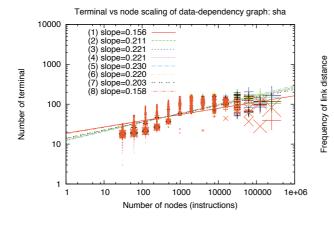

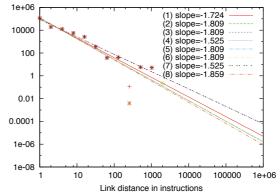

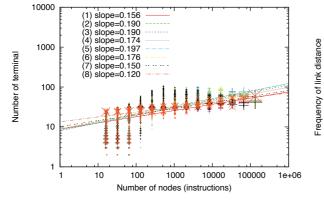

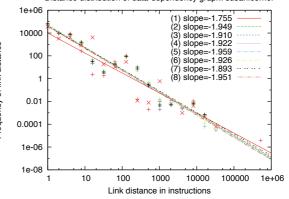

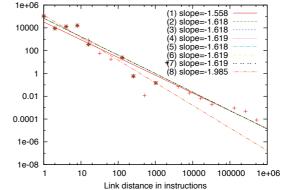

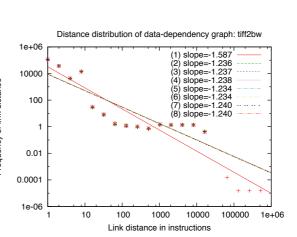

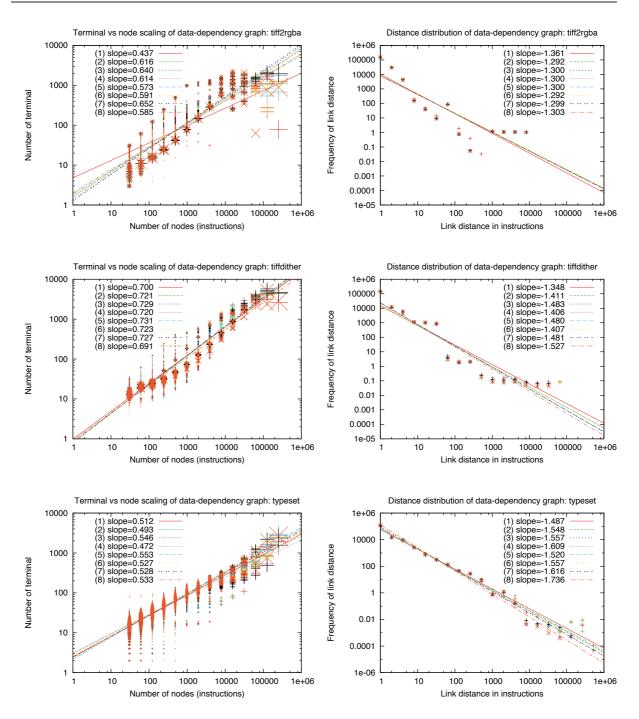

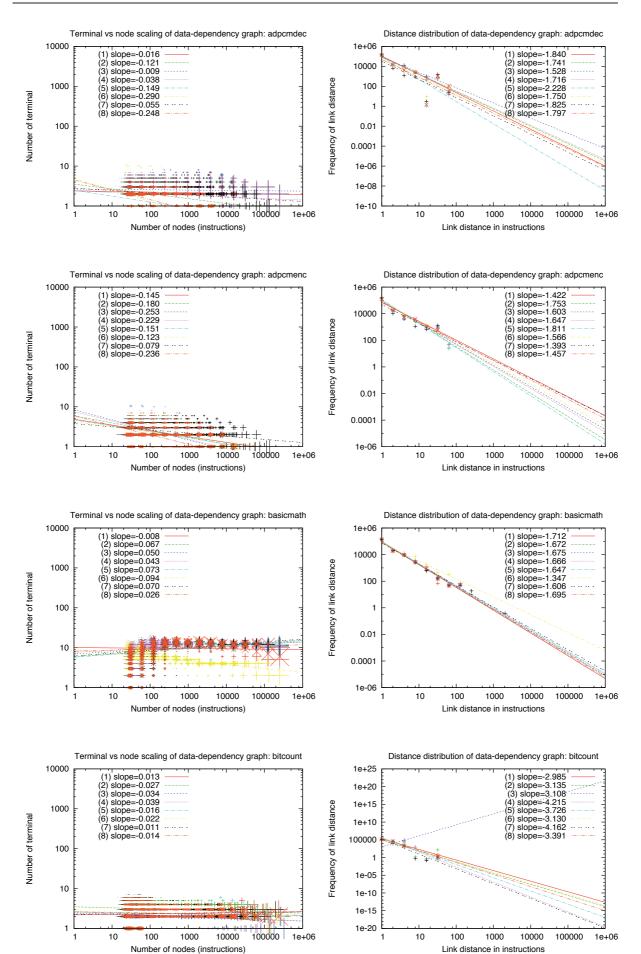

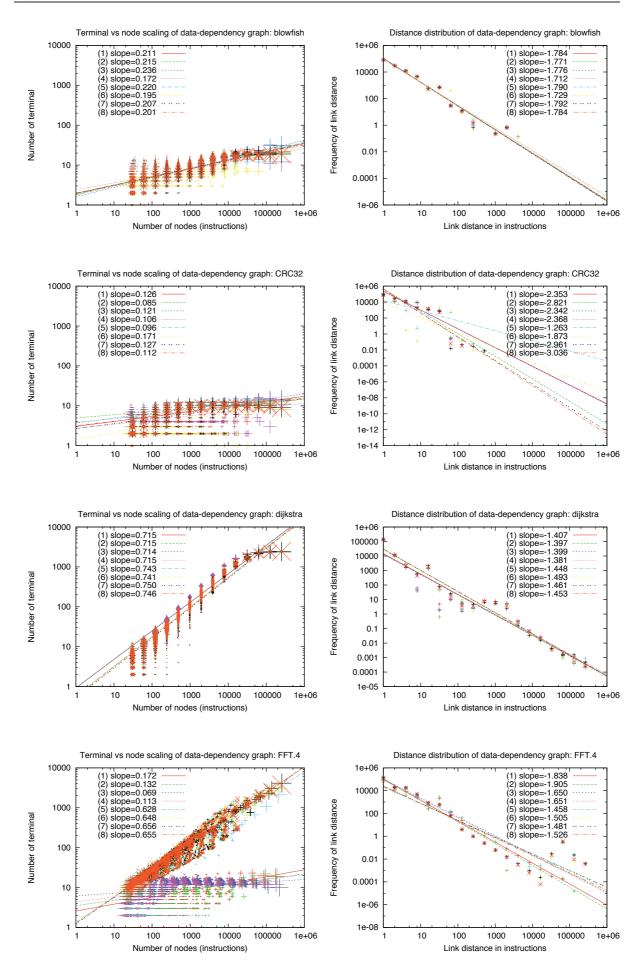

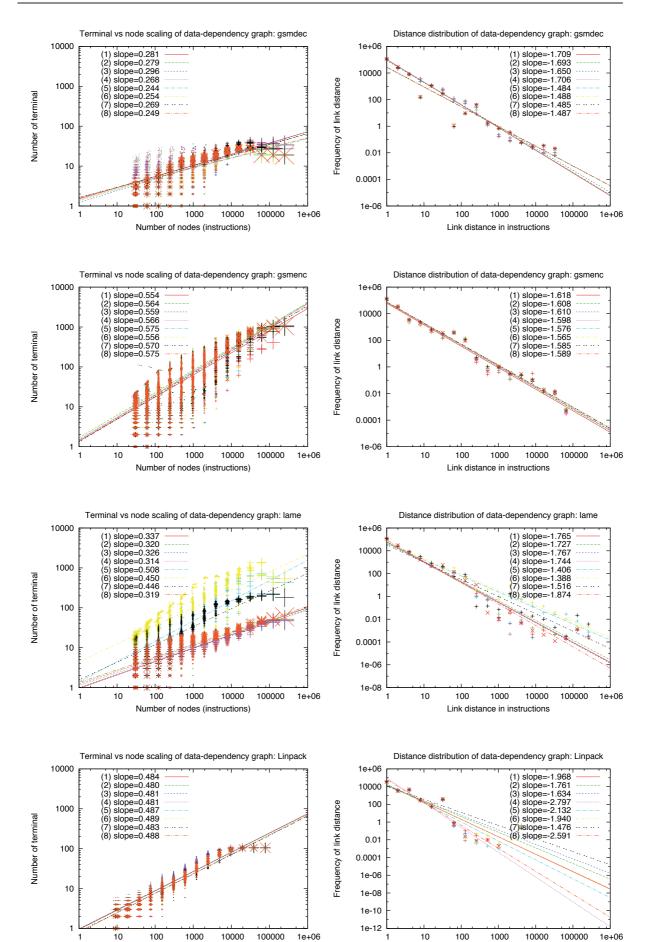

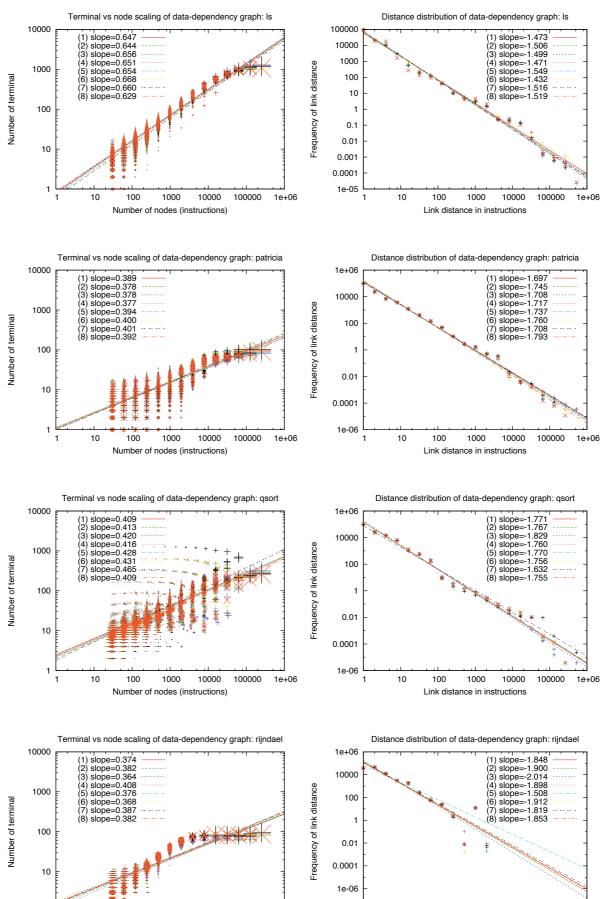

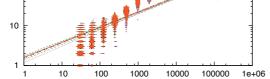

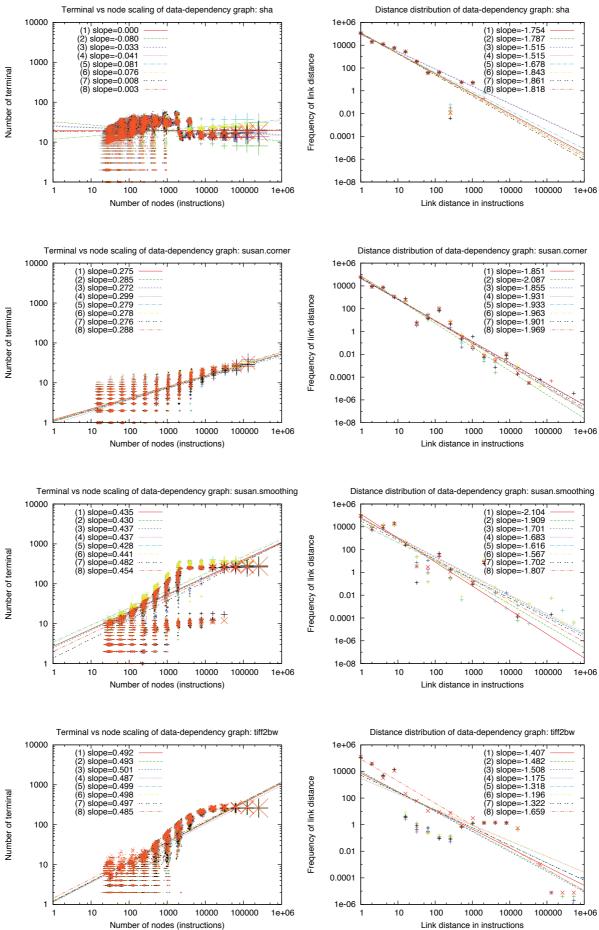

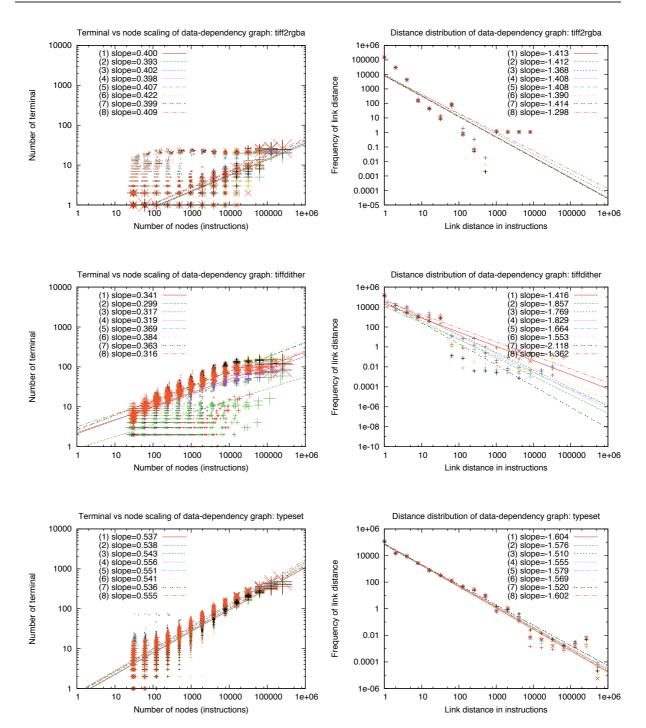

| 5.11 | A small selection of Rentian fits and their temporal-distance distributions. For a complete set please refer to Appendix C                                                                                                                                                                                                                                                                                                                             |

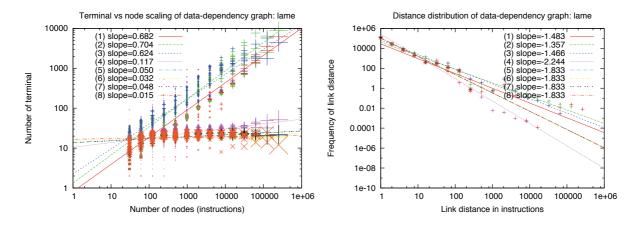

| 5.12 | Heterogeneity in the <i>lame</i> benchmark across different times. Two main Rentian scaling distributions can be seen with corresponding effects on their distance distributions 100                                                                                                                                                                                                                                                                   |

| 5.13 | Abrupt change in scaling behaviour for <i>rijndael</i>                                                                                                                                                                                                                                                                                                                                                                                                 |

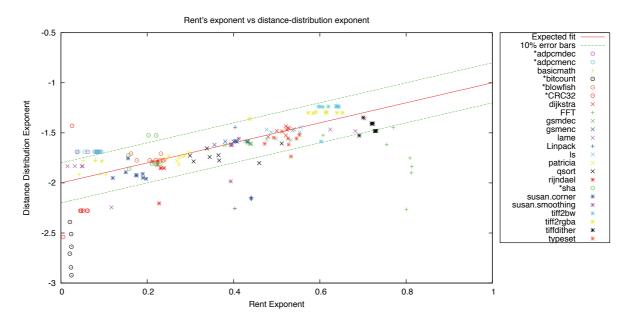

| 5.14 | Relating the Rent's exponent to the distance distribution exponent. For a Rentian network that is optimally embedded in 1-dimension (in this case 'time'), then we expect the Rent's exponent $p$ and distance distribution exponent $-\mu$ to be related by $p + \mu \approx 2$ . The ten percent error bars are shown for the sum                                                                                                                    |

| 5.15 | Selection of benchmarks chosen for comparison with the physical analysis                                                                                                                                                                                                                                                                                                                                                                               |

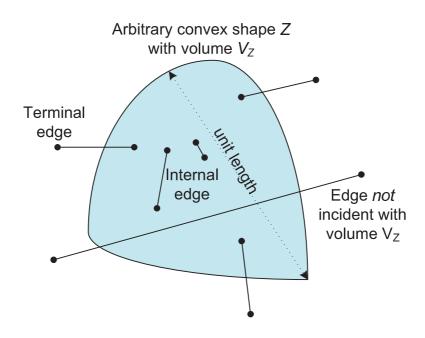

| 6.1  | Example of an arbitrary convex shape in 2-D                                                                                                                                                                                                                                                                                                                                                                                                            |

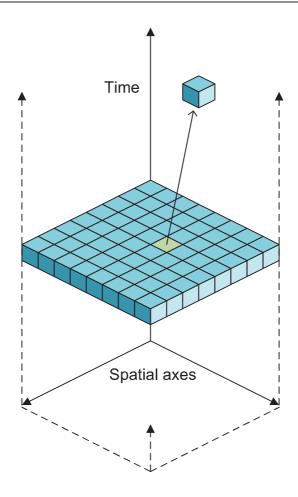

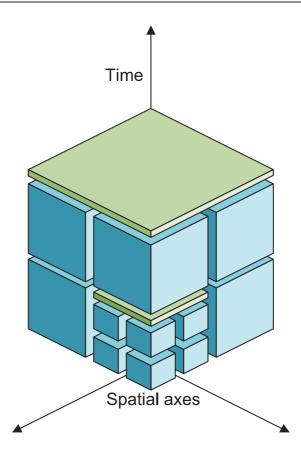

| 7.1  | Simple Spatio-Temporal view of a 64-core tiled CMP. Information flows both spatially and temporally. The cores for one moment in time are shown here. One of these cores (green) has a communication link to a future instruction on another core                                                                                                                                                                                                      |

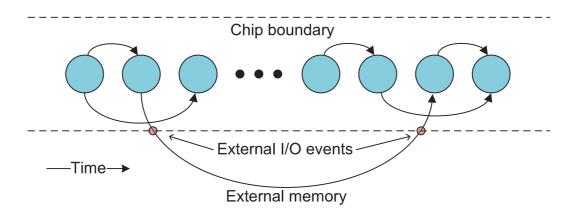

| 7.2  | Illustrating how long temporal-interconnects go off-chip, thereby inducing external I/O. Here the nodes are instructions, and the arrows between them represent data-flow, with a large temporal gap between nodes represented by ellipses. This example is with a single core, but there can be many cores in parallel, with data flowing to other instructions in the same core, or to other cores, and via external memory                          |

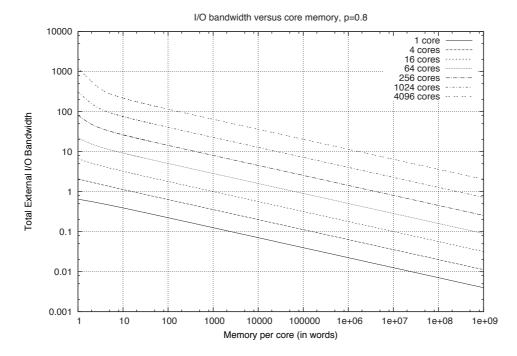

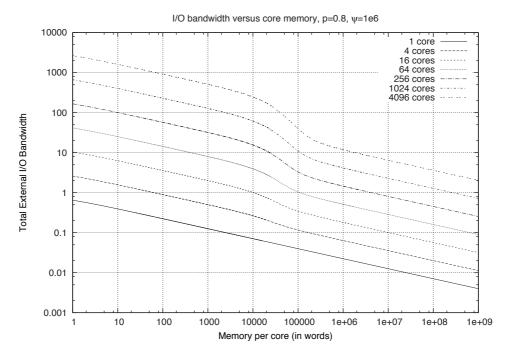

| 7.3  | Numerical evaluation of model illustrating how external I/O bandwidth scales with the number of cores and the memory per core for a 2-D mesh CMP. Note that this is asymptotic behaviour with an unbounded 'working-set' size, and excluding 'compulsory misses' where new data is fetched into on-chip memory for the very first time. An I/O bandwidth of one, here, equates to one read/write access per instruction                                |

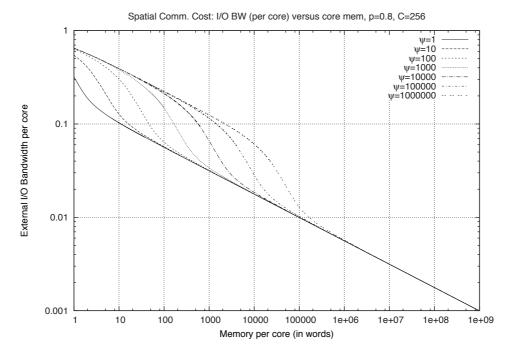

| 7.4  | Numerical evaluation of impact of coarser-grain spatial-communication parameter $\psi$ . An I/O bandwidth per-core of one, here, equates to one read/write access per instruction 152                                                                                                                                                                                                                                                                  |

| 7.5 | Numerical evaluation of model illustrating how external I/O bandwidth scales with the number of cores and the memory per core for a 2-D mesh CMP. Note that this is asymptotic behaviour with an unbounded 'working-set' size, and excluding 'compulsory misses' where new data is fetched into on-chip memory for the very first time. An I/O bandwidth of one, here, equates to one read/write access per instruction                                                                                                                                                                                                                                                                                        | .53 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

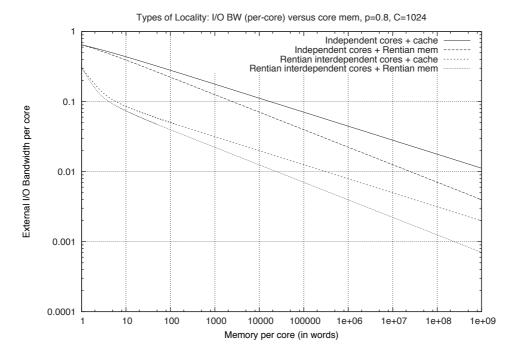

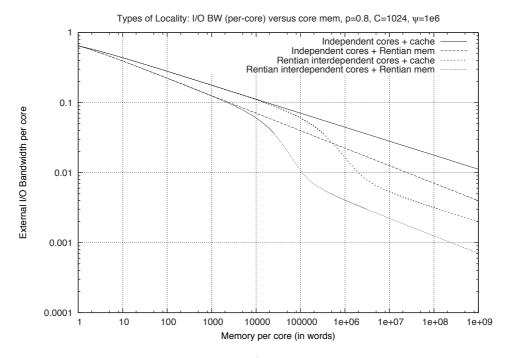

| 7.6 | Numerical evaluation of model at $\psi = 1$ , demonstrating the effect of using Rentian Memory vs. Cache model, and of interdependent vs. independent cores. An I/O bandwidth per-core of one, here, equates to one read/write access per instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .56 |

| 7.7 | Numerical evaluation of model at $\psi = 10^6$ , demonstrating the effect of using Rentian Memory vs. Cache model, and of interdependent vs. independent cores. An I/O bandwidth per-core of one, here, equates to one read/write access per instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57  |

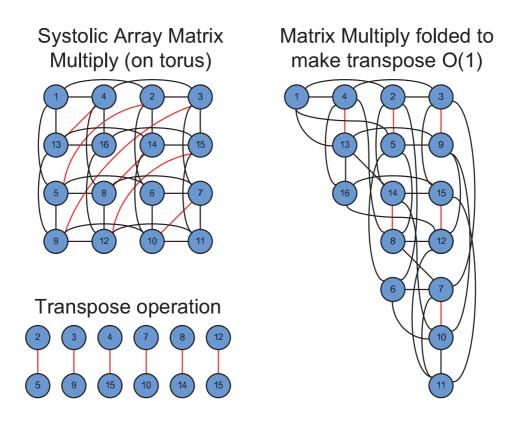

| 8.1 | Optimal embeddings don't compose. An optimal <i>spatial</i> embedding of $N \times N$ square matrix multiplication leads to a systolic array with torus topology, however optimal embedding for the transpose operation has different needs. Transpose <i>within</i> the torus results in non-local links of Manhattan-metric length $2(N-1)$ , thus growing as $O(N)$ . The matrix multiply can be folded along the diagonal to produce an $O(1)$ cost transpose operation, with further $O(1)$ dilation of matrix multiply links. (It can even be folded again to reform a square placement.) However as there are $N^3$ communication operations using these links, this can actually make total cost worse | .68 |

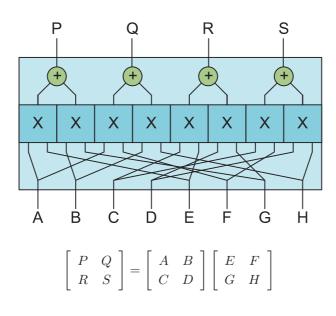

| 8.2 | Decomposition of Matrix Multiply function into smaller Matrix Multiplies (denoted by X). Merge logic (additions), and sub-partitions can be placed randomly within each level of the hierarchy. Spatio-temporal interconnect may be non-local, but the non-locality is constrained to the physical domain of that partition                                                                                                                                                                                                                                                                                                                                                                                    | .71 |

| 8.3 | Hierarchical decomposition of an algorithm (matrix multiply) into space and time. Green indicates merge logic, blue indicates a lower-level of the hierarchy. An additional level of decomposition is shown for one blue box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .72 |

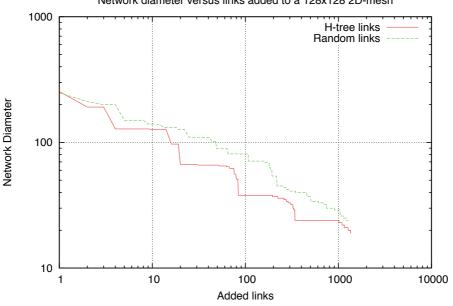

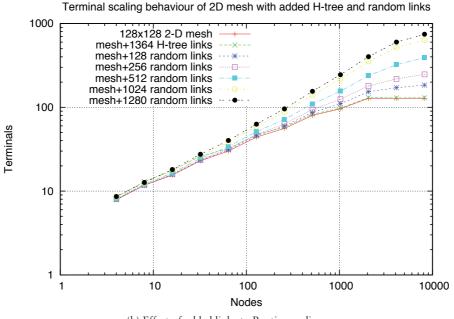

| 9.1 | Effect of adding links to network diameter and Rentian scaling. Note how the H-tree links reduce network diameter leading to a Small-World network, and yet largely preserve the fractal Rentian scaling properties of the underlying 2D mesh. In contrast, the random links disrupt the Rentian scaling                                                                                                                                                                                                                                                                                                                                                                                                       | .90 |

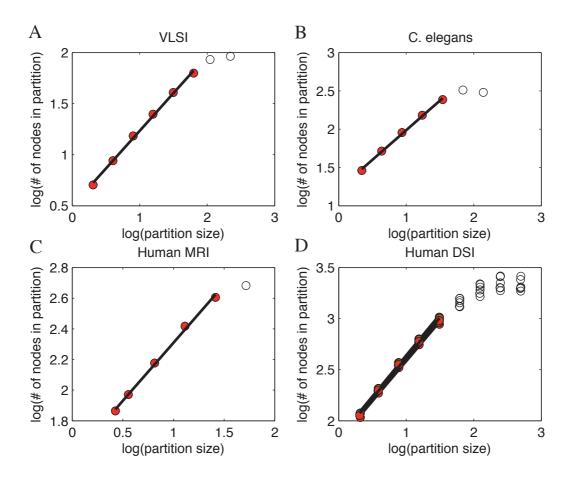

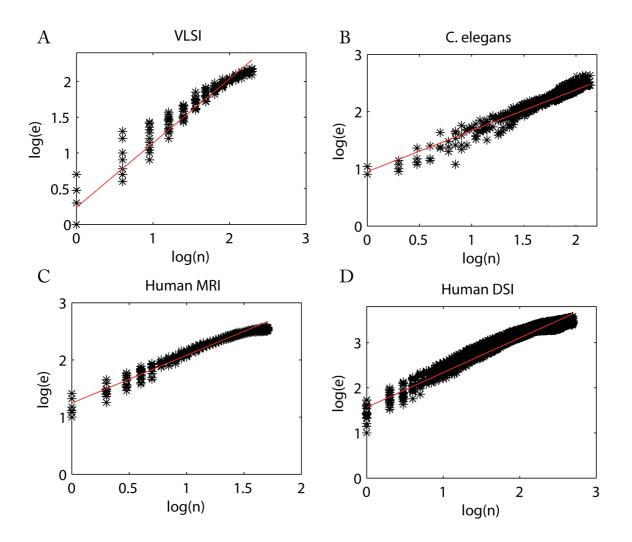

| 9.2 | Topological Rentian scaling observed in datasets $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92  |

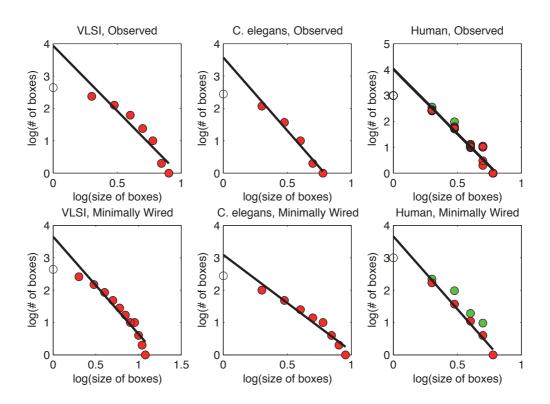

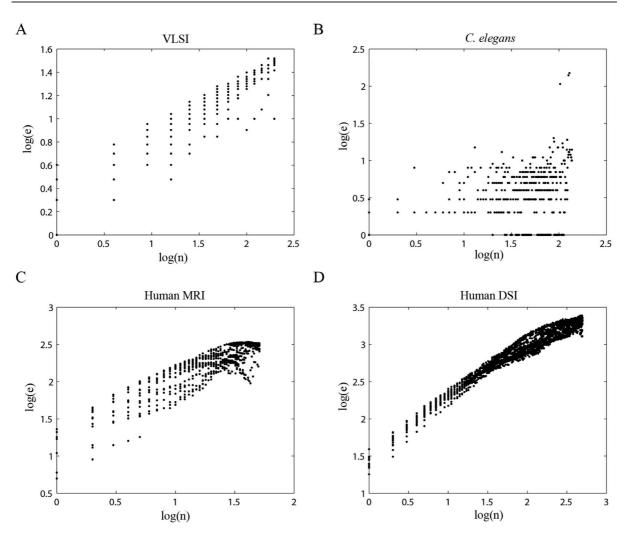

| 9.3 | Box-counting measures on the topological and minimally-rewired datasets. For Human dataset, the green dots are from MRI and the red are from DSI. The randomly-rewired dataset provided too few points to be meaningful so are not shown here                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .93 |

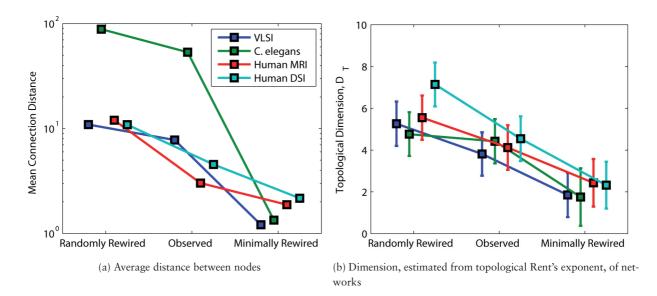

| 9.4 | Comparison of observed, minimally rewired and randomly rewired network properties 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

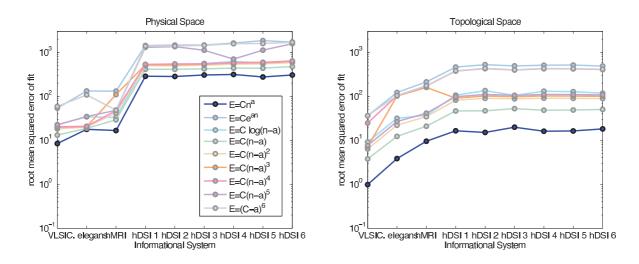

| 9.5 | Comparison of RMS errors in fit across multiple two-parameter models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 9.6 | Observed physical Rentian scaling for the datasets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95  |

| 9.7 | Scaling property of minimally re-wired networks. Rentian scaling is disrupted in C.elegans, and dispersed in the VLSI and MRI datasets. The DSI dataset still exhibits relatively tight scaling but with Rent's exponent $0.68$ which is close to the expected value of $2/3$ for a 3-D                                                                                                                                                                                                                                                                                                                                                                                                                        | 07  |

| 00  | network embedded in 3-D space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 9.8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11  |

## LIST OF TABLES

| 53<br>64<br>anerjee and                          |                                                                                                                      |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                  | 1                                                                                                                    |

| anerjee and                                      |                                                                                                                      |

| 66                                               | 5                                                                                                                    |

| mode routers. 72                                 | 2                                                                                                                    |

| ore threads                                      | 3                                                                                                                    |

| isks denote<br>to cores 89                       | )                                                                                                                    |

| and $D_T$ are $\dots \dots \dots \dots \dots 19$ | 2                                                                                                                    |

| properties.<br>es both fit-<br>19                | 97                                                                                                                   |

| or<br>isk<br>co<br>inc<br>p<br>es                | $\dots \dots $ |

### GLOSSARY

| C.elegans | Short for Caenorhabditis elegans, or the 'nematode worm'. | This is a model |

|-----------|-----------------------------------------------------------|-----------------|

|           | organism often used in biology.                           |                 |

|           |                                                           |                 |

- **CMP**..... Chip Multiprocessor, consists of multiple processors on a single chip (or stacked die).

- **Configuration Space** Concept originally from Physics where configurations of objects correspond to a position in a high-dimensional space. For example the configuration phase space of a particle is the 6-dimensional position correponding to its 3-dimensional spatial position and 3-dimensional momentum.

- **DSI**..... Diffusion Spectrum Imaging. A neuro-imaging technique that maps myelinated axons by following the diffusion of water molecules as seen by MRI machines.

- Grey Matter ...... Grey matter corresponds mainly to neurons, their synapses and unmyelinated axons. Computation occurs at neurons and synapses, so grey matter is representative of computation.

- **NoC**..... Network-on-Chip. These are communication-networks that allow the general transport of data between different parts of a computer chip.

- **Rent's Rule**..... A power-law relationship between the I/O terminals at a boundary, and the amount of logic inside the boundary.

- VLSI Very Large Scale Integrated circuits or commonly referred to as 'computer chips', but with 'very large' numbers of devices/transistors on the chip.

- White Matter ...... White matter corresponds mainly to myelinated axons. These axons are projections for long-distance communication between neurons and protected by a white sheath of myelination, so white matter is representative of communication.

# CHAPTER ONE INTRODUCTION

#### 1.1 Overview

We are entering an exciting new time in computing, where communication costs dominate over the raw computational costs. Old assumptions and models of computational complexity that assume cheap communication need to be seriously revisited in an era when moving a word of data from one part of a chip to another can consume a hundred times the energy of 32-bit arithmetic operations. This thesis argues that it is the communication costs of algorithms, rather than their computation costs, that will dominate future computing concerns. That, as we move to thousands of cores on a chip, the physical spatial locality of computation and data becomes critical to performance and cost. However, there is very little in the way of theory, models or even characterisation of such locality for Chip-Multiprocessors (CMP). This thesis adapts and extends the existing theory and models of wire locality in VLSI circuits to the physical and temporal locality of software running on CMPs. It aims to provide a new foundation for characterising, modelling, predicting and exploiting the communication properties of software, which as we show, exhibits Rentian fractal scaling. In doing so, it lays a new communicationcentric foundation for CMP software and hardware, and provides fundamental insights into their continued technological scaling.

#### **1.2 Main Contributions**

Here, the main contributions of the thesis are listed. Those in bold are considered to be particularly important contributions of the thesis.

Arguments of how the communication costs of algorithms are becoming more important than their computational costs:

- Demonstrating that non-local communication patterns such as uniformly-random traffic, and transpose traffic lead to unacceptable growth in communication cost with technology scaling.

- Showing how available external I/O bandwidth scales poorly per-core, implying that data-independent parallelism is not scalable compared to data-*inter*dependent parallelism.

Examining Rent's rule for the Network-on-Chip domain:

- A bandwidth version of Rent's rule is introduced, with a corresponding hop-length distribution for traffic that characterises the spatial locality of communication. Also, the scaling behaviour of Networks-on-Chip traffic is determined from this model, and the distribution of expected types of router operations is shown.

- To exploit this locality, a simple fault-tolerant router is introduced by a wrapper that bypasses all router logic, but allows through-traffic to continue in the same direction.

- New analytical methods employing the hop-length distributions, are demonstrated to evaluate and compare router designs for fault-tolerance behaviour under Rentian, exponential and random-traffic models. The traffic model is shown to make large differences to the fault-tolerance of designs, and can affect the choice of a suitable router.

Existing software benchmarks for CMP and single-threaded execution are examined to see if they exhibit Rentian scaling:

- SPLASH-2 and Parsec benchmarks are rigorously analysed on a 32-node CMP simulator, with many shown to demonstrate Rentian scaling, with better fits compared to other candidate distributions. Hop-length distributions, and average bandwidth for these benchmarks are shown to be predicted well, compared to a null hypothesis model.

- The dynamic-data-dependence graphs (DDDG) extracted from traces of the MiBench single-threaded benchmarks are analysed for fractal dimensionality by box-counting, where many are again shown to have fractal scaling.

- Applying Rentian analysis to the temporal domain, where the dynamic-data-dependence graphs are analysed for physical Rentian scaling based on their instruction time, and

shown to have Rentian scaling and clear evidence of this structure. Some evidence is also shown that the inter-access time distribution is related to the Rent's exponent in the predicted manner.

• The dynamic-data-dependence graphs are analysed for topological Rentian scaling and many are again shown to exhibit Rentian scaling.

New theorems are derived for Rent's rule, extending it to more general domains:

- Proof of asymptotic equivalence between Rent's rule and power-law distance distributions in homogeneous *d*-dimensional vector space, thus generalising Rent's rule beyond the 2-D Manhattan metric domain of VLSI, to arbitrary finite-dimensional vector spaces.

- Cost-universality as applied to distance distributions, where for a given head distribution, the optimal power-law tail exponent is shown to be the same under any strictly increasing cost-function.

- That optimally embedding in any *d*-dimensional space is equivalent to embedding in a configuration space where scaling parameters become independent of dimensionality. This allows Rent's rule to be generalised by extending to arbitrary configuration spaces, including the Spatio-Temporal domain of CMP.

A model for the scaling characteristics of CMP based on the generalised Rent's rule, using Spatio-Temporal interconnects:

- Derivation of a Spatio-Temporal CMP model of communication on-chip, off-chip and though a 'Rentian' memory that optimally minimises off-chip communication.

- Relations derived of how external I/O bandwidth scales with number of cores, onchip memory, granularity of communication and Rent's exponent, which should assist in the architectural exploration of CMP configurations.

- A comparison is made of caches to the perfect 'Rentian memory', which result in bounds on the performance improvement that a scratchpad memory can feasibly attain compared to caches.

- Scaling laws for optimum tradeoff between number of cores and memory, given I/O limited performance and growth.

- A comparison of scaling characteristics of data-independent parallel algorithms versus data-*inter* dependent parallel algorithms that obey Rent's rule, showing relatively large reductions in external I/O bandwidth at the thousand-core era by leveraging interdependent parallelism.

Asymptotic characterisation of communication in software:

- Demonstrating direct extraction of Rent's parameters from sample algorithms: matrix multiplication, sequential Fibonacci, Fast-Fourier Transform.

- The asymptotic cost of communication is derived for Rentian software, given the Rent's exponent and embedding domain.

- It is shown that, in software, optimal embeddings do not themselves compose to form optimal embeddings, thus posing the question of whether Rentian scaling properties can be practically preserved upon composition. This is resolved by proving that hierarchically composed/decomposed embeddings, although not optimal, preserve Rentian scaling at only a (small) constant factor penalty compared to optimal embeddings.

- A model of spatially distributed data accesses, showing how the power-law distribution of memory-access can restore constant factor or logarithmic average access costs, depending on the exponent.

Examining Rentian scaling in neuronal networks – as a natural parallel computing system at scales beyond existing technology:

- Demonstrating that the human brain and the nematode worm have neuronal networks with Rentian scaling.

- Illustrating that small-world networks are fully compatible with fractal Rentian scaling with a worked example.

- Deriving a relationship between Rentian scaling parameters within a brain, to predict the allometric scaling properties of white-matter versus grey-matter across a range of mammalian brains, and showing that the parameters extracted for Rentian scaling within the human brain correctly predict the allometric scaling properties across mammalian brains.

#### 1.3 Organisation

The research that comprises this thesis was not arrived at as a simple linear exploration. New analysis lead to new insights, and old ones had to be revisited. Whilst every effort has been made to make chapters have a consistent theme of exploration, this has come at the expense of ordering. In particular, the concepts of spatio-temporal interconnect are introduced in Chapter 5 and used in Chapter 7 for derivation of a Spatio-Temporal Rentian model for CMP. However, this model is tested experimentally on benchmarks in Chapter 5.

Chapter 1 comprises this overview.

*Chapter 2* argues that communication costs rather than purely computational ones will start to dominate power, performance and other measures with technological scaling. It shows how communication costs in the Chip Multiprocessor (CMP) domain are fundamentally different to those in the traditional parallel-computing domain, and that old intuition and solutions from the parallel-computing domain lead to poor, unscalable solutions for the CMP domain.

*Chapter 3* discusses existing models of computation, of communication, and discusses the role of the fractal scaling known as *Rent's rule* in VLSI.

*Chapter 4* argues for a bandwidth version of Rent's rule for communication over a Network-on-Chip, and examines its implications for Network-on-Chip design and fault-tolerance.

*Chapter 5* examines experimental evidence using multiple methodologies and shows that many existing software benchmarks obey the fractal scaling of Rent's rule.

*Chapter 6* takes the theory of Rent's rule beyond VLSI placement. It consists of theorems showing that Rent's rule is asymptotically equivalent to power-law-tailed distance distributions. It shows that Rent's rule applied to homogeneous spaces preserves an invariant in an equivalent configuration-space. Preserving this invariant allows a consistent generalisation of Rent's rule beyond homogeneous two- or three-dimensional spaces.

*Chapter* 7 utilises the generalisation from Chapter 6 to derive expressions for the scaling characteristics of CMP, based on the number of cores, the Rent's exponent of software, the amount of on-chip memory, and the granularity of communication. Surprisingly as the number of cores increases, there is pressure for inter-core communication to become more fine-grained.

*Chapter 8* demonstrates how one can calculate the asymptotic cost of communication for sample algorithms by direct analysis, supplanting usual measures of computational complexity. It introduces the 'embedding problem', whereby optimal embeddings do not

themselves compose optimally, and gives a simple solution that allows algorithms to be composable, and yet also preserve Rentian scaling. It then derives lower-bounds for the spatial-communication component of memory accesses.

*Chapter 9* looks at the brain as a proof-of-existence of parallel computing system at scales beyond existing technology, and demonstrates that the human brain also obeys Rent's rule. Furthermore, it shows how Rentian scaling has been preserved across the evolution of mammalian brains, as the allometric scaling of white matter to grey matter across mammals can be predicted by the self-similar Rentian scaling within the human brain. In the computing domain, this implies that Rentian scaling will likely continue to govern communication in computation at far larger scales of integration.

Chapter 10 briefly concludes and discusses potential future work.

*Appendix A* contains plots of the SPLASH-2 and PARSEC benchmark applications showing best-fits of Rentian and alternative models and a comparison of their predicted versus actual hop-length distributions.

*Appendix B* comprises plots of box-counting fractal scaling behaviour for the MiBench benchmark applications.

*Appendix* C comprises plots of physical Rentian scaling and their temporal-distance distributions for the MiBench benchmark applications.

*Appendix D* comprises plots of topological Rentian scaling and their temporal-distance distributions for the MiBench benchmark applications.

*Appendix E* describes in more detail the model used to determine best-fit parameters for the Spatio-Temporal Rentian model of a 32-core system, the results of which are in Chapter 5 and Appendix A.

*Appendix F* lists source code for numerically evaluating the Spatio-Temporal Rentian model for I/O bandwidth versus Rentian memory seen in Chapter 7.

#### 1.4 Publications

#### Peer reviewed publications

D. Greenfield, A. Banerjee, J-G. Lee, S.W. Moore, *Implications of Rent's Rule for NoC Design and Its Fault-Tolerance*, First International Symposium on Networks-on-Chip, May 2007

(Contributes to Chapters 2 and 4)

**D. Greenfield**, S.W. Moore, *Fractal communication in software data dependency graphs*. Symposium on Parallel Algorithms and Architectures, June 2008

(Contributes to Chapter 5)

**D. Greenfield**, S.W. Moore, *Implications of Electronics Technology Trends to Algorithm Design*. 'Visions of Computer Science' BCS International Academic Conference 2008, *and also as:* The Computer Journal, British Computer Society, Volume 52, Number 6

(Contributes to Chapters 2 and 5)

D. Bassett, D. Greenfield (joint first author), A Meyer-Lindenberg, D. Weinberger, S.W. Moore, E Bullmore, *Efficient Physical Embedding of Topologically Complex Information Processing Networks in Brains and Computer Circuits*, PLoS Computational Biology, April 2010

(Contributes to Chapter 9)

#### Invited paper

S.W. Moore, D. Greenfield, *The Next Resource War: Computation vs. Communication*. System Level Interconnect Prediction, June 2008

## CHAPTER TWO MOTIVATIONS: COMMUNICATION VS. COMPUTATION

For most of the history of computer science, computation has been 'expensive' and communication practically 'free'. This fundamental, and yet implicit assumption, underlies our analysis of algorithms, and guides our intuition when constructing solutions to problems in Computer Science. Unfortunately, this assumption has been eroded with technological scaling as we can no longer 'hide' the underlying laws of physics. Indeed, the tables have turned – as we shall show, it is now communication that has become expensive whilst computation is practically 'free'. We shall show that looking forward, it is the communication of algorithms rather than their computation that will become the dominant factor in energy consumption, cost and performance metrics in the many-core era.

#### 2.1 Broken assumptions: no escape from Physics

The exponential growth of transistor density, as predicted by Moore's law, has allowed transistors to scale over the last 35 years from dimensions of 10,000nm (Intel 4004) to 45nm (current Intel and AMD processors). This dramatic growth in transistor density has allowed processors to scale in complexity from the 2300 transistors of the Intel 4004, to the 731 million transistors of the Intel Core i7 (including cache). During this period, however, chip sizes have largely been unchanged at about 10-20mm on a side, depending on cost. While transistors have been getting smaller and faster, the wires that connect one region of the chip to another, have not scaled. Relative to transistors, they have gotten exponentially worse in speed, power, and manufacturing cost.

In table 2.1 we see how technology scaling affects the relative cost of communication versus computation. This table is adapted from a presentation given by Dally [34]. We can see that communication is no longer inexpensive – thanks to decades of technological scaling, even at the older 130nm scale, merely transferring 32-bits of data from one

| technology node          | 130nm CMOS  | 45nm CMOS    |

|--------------------------|-------------|--------------|

| transfer 32b across-chip | 20 ALU ops  | 57 ALU ops   |

| transfer 32b off-chip    | 260 ALU ops | 1300 ALU ops |

Table 2.1: Comparing trends in energy consumption, adapted from Dally [34]

part of the chip to another consumes the equivalent of 20 ALU operations. Moreover, at current scales of 45nm, it is even worse, and this disparity will continue to grow exponentially with technological scaling. Furthermore, we see that in order to transfer data off-chip, the costs become even steeper, with large transistors required to drive the pins. To some extent, new technologies can help mitigate these, but as we shall see, they do not halt the larger trend. What this means is that communication, both on-chip and particularly off-chip, can be many orders of magnitude more expensive than computation.

Computer Architects have done a remarkable job insulating software engineers from the changes due to technological scaling. They have kept the illusion of ever faster serial-processors alive until recently, when diminishing returns to instruction-level parallelism, excessive power-consumption costs and slow on-chip interconnect, have resulted in abandoning this illusion, and forced software engineers to move to multi-core scaling. Whilst computer scientists rush to cushion this blow, by trying to make parallel programming easier, they need to be aware that more challenges from technological scaling are waiting in stall, that they cannot be insulated against.

With continued technological scaling, we are transitioning into an era with thousands or even millions of cores. With so many cores, one might even say that 'processors are the new transistors'. Software and instructions can no longer be thought of as operating in some sort of Platonic realm. Software, and data, instead have a physical spatial position. Instructions are actually executed at some physical position, and data needs to be stored and retrieved from a physical position and transported to another physical position. This has profound implications for the future of software design.

Suppose two algorithm designers Alice and Bob construct their own data-structure to store and retrieve information. As there is too much data to fit on one core, it necessarily spills over to the memory of surrounding cores (or even a neighbourhood of memories, off-chip). This can be much like the binary tree traversal in figure 2.1. Here colours correspond to the level of the tree. Although binary tree traversal is thought of as  $O(\log N)$  this is only the case if communication costs are ignored. A physical implementation necessarily has the data reside somewhere, and this limits the spatial locality. If the nodes are placed randomly but in the 2-D neighbourhood of the root node, then on average each traversal of the tree takes time  $O(\sqrt{N})$ , resulting in a total time of  $O(\sqrt{N} \log N)$ . If nodes are carefully placed in two dimensions (such as at the bottom of figure 2.1), then the average distances between levels of the binary tree hierarchy grows exponentially, but traversal takes time  $O(\sqrt{N})$ . Thus even if Bob carefully produced an algorithm that has

Figure 2.1: Algorithms and data-structures must be physically embedded in space (here the 2-D space onchip). Asymptotic tree traversal costs are shown for binary tree placements, assuming that traversal costs are proportional to distance.

computational complexity  $O(\log N)$ , Alice could produce a poorer computational complexity algorithm of  $O(\sqrt{N})$  but focused on communication costs, and asymptotically outperform Bob's algorithm. Indeed, in general, Alice will do no worse than Bob by focusing on communication complexity, but can also do better than Bob as here. We will show in Chapter 8, that the asymptotic scaling of communication costs is at best equal to the asymptotic scaling of computational costs, and can typically be worse. This may mean that communication complexity may one day replace computational complexity as the measure of asymptotic scaling in algorithms.

#### 2.2 The many-core memory bandwidth wall

We noted (see Table 2.1) that communication power off-chip is not scaling with transistor performance. Despite this, rather than using less I/O bandwidth, demand for I/O bandwidth is growing, and technology is not keeping up. Figure (2.2) shows the estimated growth for total chip I/O bandwidth based on ITRS predicted figures [59] for pin-count in their 'cost-performance balanced' model and the predicted bandwidth growth of high-

Figure 2.2: ITRS I/O Bandwidth Growth

Figure 2.3: Predicted scaling of I/O Bandwidth per Core using ITRS numbers, based on 2x cores per generation or 1.4x cores per generation

speed pins. We note that after 2017 the growth changes to a more conservative trend as manufacturable solutions for these are not currently known. The rate of growth can be shown by fitting a range of Rent's bandwidth-exponents (Rent's rule is discussed in Chapter 3, and the bandwidth version explained in Chapter 4). These are estimated for the years up to 2017, yielding exponents between 0.57 to 0.67, depending on pin-count growth rates.

We should note that these numbers may not account for the power and thermal constraints that are also present on the system that may prevent pin counts and pin bandwidth from growing as fast as this. Also, the size of I/O pads and drivers do not tend to change much with each process generation, so the exponential growth in pin count may have other costly repercussions for die size. Optical off-chip communication may help improve available bandwidth, which is discussed further below, however it is unlikely to be a panacea.